USER'S MANUAL

# PXI INDUSTRYPACK CARRIER

MODEL PX403S

#### COPYRIGHT

C&H Technologies, Inc. (C&H) provides this manual "as is" without warranty of any kind, either expressed or implied, including but not limited to the implied warranties of merchantability and fitness for a particular purpose. C&H may make improvements and/or changes in the product(s) and/or program(s) described in this manual at any time and without notice.

This publication could contain technical inaccuracies or typographical errors. Changes are periodically made to the information herein; these changes will be incorporated in new editions of this publication.

#### Copyright © 2000 by C&H Technologies, Inc.

The information and/or drawings set forth in this document and all rights in and to inventions disclosed herein which might be granted thereon disclosing or employing the materials, methods, techniques or apparatus described herein, are the exclusive property of C&H Technologies, Inc.

A Reader's Comment Form is provided at the back of this publication. If this form has been removed address comments to:

C&H Technologies, Inc. Technical Publications 445 Round Rock West Drive Round Rock, Texas 78681-5012

C&H may use or distribute any of the information you supply in any way that it believes appropriate without incurring any obligations whatever.

#### **MODULE WARRANTY**

C&H Technologies, Inc. warrants its products to be free from defects in material and workmanship for three years from date of shipment. C&H will repair or replace the defective product without charge within the warranty period, provided the defective item is shipped, freight prepaid, to C&H Technologies, at 445 Round Rock West Drive, Round Rock, Texas 78681. C&H will pay return freight charges to any point in the continental United States or Canada.

Obligations under this warranty shall be limited to repair or replacement, at C&H's discretion, of any product or part thereof which has been returned by the original purchaser with transportation prepaid and, upon examination by C&H, found to be defective. C&H assumes no responsibility for loss or damage to equipment being returned for repair or replacement under the terms of this warranty. Equipment, which, upon examination by C&H, requires repair or replacement of parts thereof as a result of improper installation, misuse, unauthorized alterations or repairs, or user negligence, will have such repairs or replacement of parts made at then current rates.

This warranty does not cover damage caused by misuse, neglect, accident, or improper application or installation. C&H shall not be liable for consequential damages of any kind arising out of the purchase, installation, use or misuse of the product. C&H makes no representation or warranty of any kind, either expressed or implied, with respect to equipment operation or procedures. Any action that the user may take in reliance upon the operation or accuracy of this equipment shall be taken solely at the user's own responsibility and risk.

Please notify the C&H sales department to obtain a Return Authorization Number (RAN) prior to return of a product under the terms of this warranty. Notification is to include the Model and Serial numbers of the product along with full details of the problem. Modules returned should clearly show the RAN on the outside of the package.

#### **DOCUMENT REVISION NOTICE**

C&H Technologies, Inc. makes every attempt to provide up-to-date manuals with the associated equipment. Occasionally, throughout the life of an instrument, changes are deemed necessary to equipment related documentation. In order to provide our customers with the latest revision of product documentation, we have made all documents available for download from our web site, **www.chtech.com.**

### NOTE

The contents of any amendment may affect operation, maintenance, or calibration of the equipment.

# INTRODUCTION

This manual describes the operation and use of the C&H Model PX403S PXI IndustryPack<sup>®</sup> Carrier (Part Number 11027300). This module is one of a number of test and data acquisition/control modules provided by C&H.

Contained within this manual are the physical and electrical specifications, installation and startup procedures, functional description, and configuration and programming guidelines to adequately use the product.

This manual is based on a low level register access, and is written in such a manner to provide understanding to the user based on this type of access. If a driver is provided, please refer to the driver documentation for instruction using the higher level interface provided by the driver.

<sup>&</sup>lt;sup>®</sup> IndustryPack is a registered trademark of SBS Technologies, Inc.

vi

# **TABLE OF CONTENTS**

| 1.0 GENERAL DESCRIPTION                  | 1   |

|------------------------------------------|-----|

| 1.1 PURPOSE OF EQUIPMENT                 |     |

| 1.2 SPECIFICATIONS OF EQUIPMENT          |     |

| 1.2.1 Key Specifications                 |     |

| 1.2.2 Electrical                         |     |

| 1.2.3 Mechanical                         | 2   |

| 1.2.4 Environmental                      | 2   |

| 1.2.5 Bus Compliance                     | 2   |

| 2.0 INSTALLATION                         | 3   |

| 2.1 UNPACKING AND INSPECTION             | 3   |

| 2.2 HANDLING PRECAUTIONS                 |     |

| 2.3 INSTALLATION OF INDUSTRY PACKS       | 3   |

| 2.3 INSTALLATION OF CARRIER              |     |

| 2.4 PREPARATION FOR RESHIPMENT           | 4   |

| 3.0 FUNCTIONAL DESCRIPTION               | 5   |

| 3.1 GENERAL                              | 5   |

| 3.2 INTERFACES                           | 6   |

| 3.3 INDICATORS                           | 6   |

| 3.4 CONNECTORS                           | 6   |

| 3.4.1 Front Panel Connector              |     |

| 3.4.2 Rear Connectors                    | 6   |

| 4.0 OPERATING INSTRUCTIONS               | 7   |

| 4.1 GENERAL                              | 7   |

| 4.2 CONFIGURATION                        | 7   |

| 4.2.1 Hardware Configuration             | 7   |

| 4.2.2 Software Configuration             | 8   |

| 4.3 IP I/O OPERATIONS                    | 12  |

| 4.3.1 ID PROM Access                     | 12  |

| 4.3.2 I/O Space Access                   |     |

| 4.3.3 Memory Access                      |     |

| 4.2.4 Interrupts                         |     |

| 4.2.5 Triggers                           | 13  |

| APPENDIX A - CONNECTORS                  | A-1 |

|                                          |     |

| APPENDIX B - PCI CONFIGURATION REGISTERS | B-1 |

# LIST OF FIGURES

| Figure 1. | Functional Block Diagram      | 5 |

|-----------|-------------------------------|---|

| Figure 2. | Front Panel                   | 6 |

|           | Hardware Configuration        |   |

| Figure 4. | IP Address Map                | 8 |

| Figure 5. | IP Status/Control Register 1  | 0 |

| Figure 6. | IP Trigger Control Register 1 | 1 |

| -         | Trigger Functional Diagram 1  |   |

# LIST OF TABLES

| Table I. | ID PROM | Contents (Format | [) | 12 | 2 |

|----------|---------|------------------|----|----|---|

|----------|---------|------------------|----|----|---|

# **1.0 GENERAL DESCRIPTION**

The PX403S is a single slot 3U form factor PXI/Compact PCI bus compatible carrier module that provides electrical and mechanical support for up to two single wide IndustryPacks (IPs) or one double wide IndustryPack (IP). Each IndustryPack is controlled separately, and appears as an independent device in the PXI/CPCI environment.

# **1.1 PURPOSE OF EQUIPMENT**

This module provides a carrier function for a variety of industry standard plug-in modules that vary in functionality from A/D converters, analog input/output, digital input/output, serial interface, motion control, memory, networking, telecommunication, bus interface, video and many more. With over 350 different modules available in the IndustryPack format, the PX403S is ideal for providing required functions where a PXI or cPCI module does not exist, or for providing more functionality per slot. For a more complete listing of available IPs refer to the following web sites, <u>www.vita.com</u> and <u>www.groupipc.com</u>.

# **1.2 SPECIFICATIONS OF EQUIPMENT**

### **1.2.1 Key Specifications**

- □ Supports up to two (2) Industry Standard IndustryPacks

- □ Individual PCI interface for each IP

- □ Supports usage of PXI bused triggers, STAR triggers, 10MHz system clock

- □ Special trigger routing and prescaler functionality

- □ Separate Interrupt Support for each IP

- $\Box$  Isolated +5V, +12V, and -12V supplies each IP

- □ Supports 8MHz or 32MHz IPs

- □ 3U form factor

- □ Up to 100 I/O lines

- □ 33MHz CPCI compliant

- □ IP Bus Error Detection

- □ JTAG boundary scan

### **1.2.2 Electrical**

The module requires the +5V, 3.3V, -12V and +12V power from the PXI back plane. The peak module current ( $I_{PM}$ ) for the +5 volt supply is 350 milliamps and the +3.3 volt supply is 100 milliamps in addition to any current required by installed IPs. The carrier does not use the +12 and -12 volt supplies.

#### **1.2.3 Mechanical**

The mechanical dimensions of the module are in conformance with the PXI bus specification Rev 1.0 for single slot 3U-form factor Modules. The nominal dimensions are 100.0 mm (3.94 in) high x 160 mm (6.3 in) deep. The module is designed for a mainframe with 20.32 mm (0.8 in) spacing between slots. As required by the PXI bus specification, these dimensions are in accordance with those given in the CPCI bus specification (PICMG 2.0 Rev 2.1).

#### **1.2.4 Environmental**

The environmental specifications of the module are:

| Operating Temperature: | $0^{\circ}$ C to +55°C             |

|------------------------|------------------------------------|

| Storage Temperature:   | $-40^{\circ}$ C to $+75^{\circ}$ C |

| Humidity:              | <95% without condensation          |

#### **1.2.5 Bus Compliance**

The PX403S module complies with the following Specifications.

| PCI Bridge Specification: | Revision 1.0                                   |

|---------------------------|------------------------------------------------|

| PCI Specification:        | Revision 2.1                                   |

| PXI Specification:        | Revision 1.0                                   |

| CPCI Specification:       | PICMG 2.0 R2.1                                 |

| IP Specification:         | ANSI/VITA 4-1995 IP specification Revision 1.0 |

|                           |                                                |

| Manufacturer ID:          | 162C <sub>16</sub> (C&H Technologies, Inc.)    |

| Model Code:               | 403A <sub>16</sub>                             |

| PCI Data Transfer:        | 33MHz/32-bit PCI access                        |

| IP Interface:             | 8 or 32MHz/16-bit                              |

| Interrupts:               | Full individual interrupt support              |

| Triggers:                 | Full PXI Trigger Support.                      |

# **2.0 INSTALLATION**

### 2.1 UNPACKING AND INSPECTION

In most cases, the PX403S is individually sealed and packaged for shipment. Verify that there has been no damage to the shipping container. If damage exists then the container should be retained, as it will provide evidence of carrier caused problems. Such problems should be reported to the carrier immediately as well as to C&H. If there is no damage to the shipping container, carefully remove the module from its box and anti static bag and inspect for any signs of physical damage. If damage exists, report immediately to C&H.

### 2.2 HANDLING PRECAUTIONS

The module contains components that are sensitive to electrostatic discharge. When handling the module for any reason, do so at a static-controlled workstation, whenever possible. At a minimum, avoid work areas that are potential static sources, such as carpeted areas. Avoid unnecessary contact with the components on the module.

# 2.3 INSTALLATION OF INDUSTRY PACKS

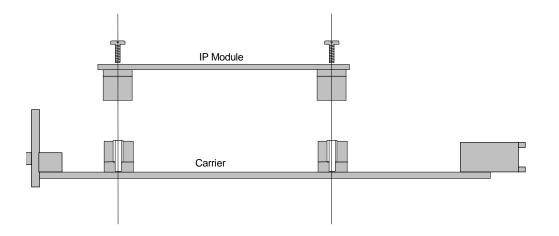

All IndustryPacks must be installed before the PX403S is installed into the PXI system. IndustryPacks are installed by firmly pressing the two connectors on the IP together with the connectors on the carrier. The connectors are keyed to insure the IP can only be installed correctly. Follow the mounting instructions provided with the IP. The IP manufacturer should have provided mounting hardware.

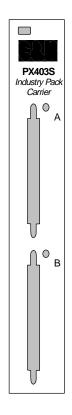

There are two possible mounting locations on the carrier: A and B. IndustryPacks may be installed into either location. Enable the IP position and memory by following the hardware configuration instructions in Section 4.2.1 Hardware Configuration.

#### **2.3 INSTALLATION OF CARRIER**

# CAUTION: Read the entire User's Manual before proceeding with the installation and application of power.

Insert the module into the desired PXI or CPCI slot. Apply power. If no obvious problems exist, proceed to communicate with the module as outlined in Section 4.0 OPERATING INSTRUCTIONS.

#### 2.4 PREPARATION FOR RESHIPMENT

If the module is to be shipped separately it should be enclosed in a suitable water and vapor proof anti static bag. Heat-seal or tape the bag to insure a moisture-proof closure. When sealing the bag, keep trapped air volume to a minimum. The shipping container should be a rigid box of sufficient size and strength to protect the equipment from damage.

# **3.0 FUNCTIONAL DESCRIPTION**

#### **3.1 GENERAL**

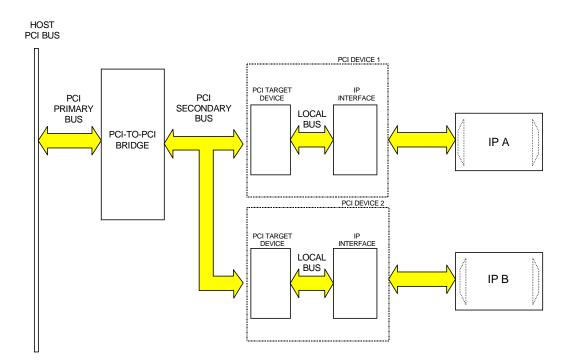

The PX403S provides a mechanical and electrical interface for up to two standard Industry Pack modules (or one doublewide module). The carrier provides access to the IndustryPack's ID PROM, I/O Space, and Memory Space(if present). To ease software integration of the individual functions provided by IP modules, the PX403S treats each IP module as an independent device. The PCI-to-PCI bridge technology implemented on the PX403S allows each IP to have individual PCI configuration registers. This allows software applications and drivers to access individual IP functions as truly independent devices. Each IndustryPack is controlled separately, and appears as an independent device in the PXI environment. A simplified functional block diagram of the module is shown in Figure 1.

The PX403S can support Type I, II, and III IP modules. Type I modules have no components on the back of the module. Type II modules have components on the back, but are subject to height restrictions. Type III module have components on the back, without height restrictions. If a Type III module is used, be sure that the IP doesn't violate the slot to slot spacing defined by the PXI or the CPCI specifications. If the IP violates the specification, population of the adjacent slot will not be possible.

Figure 1. Functional Block Diagram

# **3.2 INTERFACES**

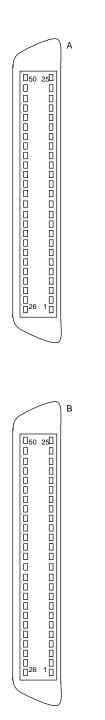

The two IP positions interface electrically and mechanically with industry standard IndustryPack modules meeting the IndustryPack Logic Interface Specification ANSI/VITA 4-1995. The IPs interface to the PX403S through one 50-pin connector mounted to the carrier board. The IP's I/O signals interface through the other 50-pin connector and are routed the front panel connector of the PX403S.

### **3.3 INDICATORS**

The appropriate LED indicator on the front panel illuminates whenever the host processor properly accesses the IP.

# **3.4 CONNECTORS**

#### 3.4.1 Front Panel Connector

The IP's 50 I/O pins are routed through the carrier board to a 50-pin (.8mm) shielded AMP Champ type connector accessible at the front panel of the PX403S. See Appendix A for pin-out details.

Board Connector AMP part number: 787096-1

Mating Cable Connector Amp part number: 787131-1

#### 3.4.2 Rear Connectors

The P1 and P2 connectors are configured in accordance with the PXI / CPCI specification. (See Appendix A)

**Figure 2. Front Panel**

# 4.0 OPERATING INSTRUCTIONS

# 4.1 GENERAL

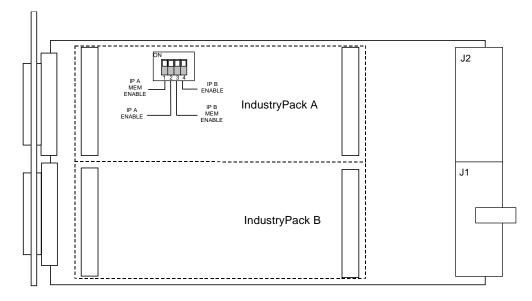

The PX403S is easily configured using a few physical switches and a variety of software registers. The switches allow access to an IP to be individually enabled or disable and allow memory to be allocated or not allocate for an IP, see Figure 3. The software registers provide individual configuration of interrupts, triggers, clock speed, and bus time out for each IP.

### **4.2 CONFIGURATION**

### 4.2.1 Hardware Configuration

NOTE: Hardware configuration must be done while power to the module is OFF.

<u>IP Modules Enable</u> There is an enable switch for each IP slot. Each switch represents an IP and must be enabled before the carrier will recognize a module as present. When the switch is in the ON position the slot is disabled. Conversely, the IP is enabled when the switch is OFF position.

<u>IP Memory Enable</u> There is a memory enable switch for each IP slot. Each IP Memory Enable switch must be enabled before the carrier will recognize that the module present requires memory. When the switch is in the ON position the slot is assigned memory. Conversely, the IP is not assigned memory when the switch is OFF position.

Figure 3. Hardware Configuration

#### 4.2.2 Software Configuration

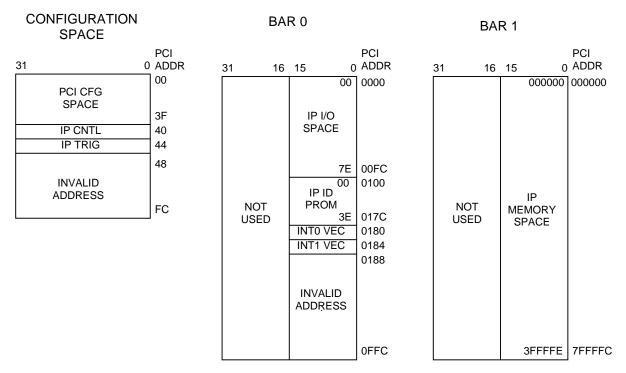

Each IP enabled on the PX403S has its own PCI Device Number and they appear as device's 1 and 2 on a subordinate PCI bus. The PX403S uses the PCI Configuration, Base Address Register 0 (BAR0) and Base Address Register 1 (BAR1) Space out of the available PCI resources.

The PX403S supports both D16 and D8 (Even/Odd) data access to the IPs. Each IP has its own PCI interface, which means that each IP is independently configured and accessed. The IP resources (ID, I/O, and Memory) are all mapped into PCI memory space. The memory space is fully decoded. If an invalid address is attempted, the PX403S will issue a target abort. The memory map is identical for each IP as indicated in Figure 4. PCI I/O space is not used.

# NOTE: Since IPs use 16-bit addressing and PCI use 32-bit addressing, multiply the IP address by two for the correct PCI address.

Note: The PCI address is two times the IP address. The upper 16bits of a 32-bit PCI read are returned as zeros. Only the lower 16-bits are used on a 32-bit PCI write.

Figure 4. IP Address Map

The PCI and interface control registers are located in the PCI device configuration space. The PCI configuration space is used to control and report information concerning the PCI interface. Most of the registers in the configuration space are used and/or set by the system BIOS. See Appendix B for reference information on these PCI configuration registers.

Several registers within the PCI configuration space are of particular interest. They are the Base Address Registers (BAR0 and BAR1) and PCI user-defined registers (IP CNTL and IP INT). All other software control of an IP is IP dependent and is described in the IP's user manual.

<u>Base Address Registers (BAR0 and BAR1)</u> (Base +  $10_{16}$  and Base +  $14_{16}$ ) BAR0 is the base address for the IP I/O Space, ID PROM, and IP interrupt vector registers. The PX403S automatically requests 4Kbytes of PCI memory space and the BIOS should allocate that amount for this address area. BAR1 is the base address for the IP Memory Space. If the IP Memory Enable switch is ON (see 4.2.1), then the PX403S will request 16Mbytes of PCI memory space and the BIOS should allocate that amount for this address area.

<u>IP Interface Status/Control Register (IP CNTL)</u> (Base  $+40_{16}$ ) This read/write register is used to control and status interface functions such as reset, clock speed, interrupts, triggers and bus timeout. See Figure 5 for details.

<u>IP Interface Trigger Control Register (IP INT)</u> (Base +  $44_{16}$ ) This read/write register is used to configure the PXI Trigger/IP strobe operation. See Figure 6 for details.

#### **IP Status/Control**

| Bit                        | 15  | 14 | 13 | 12 | 11 | 10 | 9      | 8         | 7           | 6  | 5  | 4   | 3    | 2    | 1   | 0   |

|----------------------------|-----|----|----|----|----|----|--------|-----------|-------------|----|----|-----|------|------|-----|-----|

| Write                      | CLR | _  | ID | _  | _  | Ti | me Out | (0-7)     | _           | _  | _  | CLK |      |      |     | RST |

| Read                       | INT | _  | ID |    | _  | Ti | me Out | (0-7)     |             | _  |    | CLK | IRQ1 | IRQ0 | ERR | RST |

| 42<br>Bit<br>Write<br>Read | 31  | 30 | 29 | 28 | 27 | 26 | 25     | 24<br>Res | 23<br>erved | 22 | 21 | 20  | 19   | 18   | 17  | 16  |

CLR  $\Rightarrow$  Clear PCI Interrupt Request (1 = clear PCI Interrupt Pending)

INT  $\Rightarrow$  PCI Interrupt Request (1 = interrupt pending)

ID  $\Rightarrow$  IP ID Write Enable (1 = write enabled (if IP allows writes to ID PROM))

Time Out ⇔ Bus Time Out

40

- 00h 3.2 µs

- 01h 32 µs

- 02h 320 µs

- 03h 3.2 ms

- 04h 32 ms

- 05h 320 ms

- 06h 3.2 sec

- 07h FFh Reserved

CLK  $\Rightarrow$  IP Clock Control (0= 8 MHz, 1 = 32 MHz)

- IRQ0  $\Rightarrow$  IP Interrupt Request 0 (1 = pending)

- IRQ1  $\Rightarrow$  IP Interrupt Request 1 (1 = pending)

ERR  $\Rightarrow$  IP Error Indicator (0 = OK, 1 = failure, directly reflects the IP Module Error signal)

RST  $\Rightarrow$  IP Reset (1 = reset IP, leave for >100µs then clear to 0)

#### Figure 5. IP Status/Control Register

**IP Trigger Control**

| Bit   | 15 | 14              | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6     | 5    | 4 | 3   | 2   | 1   | 0  |

|-------|----|-----------------|----|----|----|----|---|---|---|-------|------|---|-----|-----|-----|----|

| Write |    | Trig En (0 – 7) |    |    |    |    |   |   |   |       | aler |   | SEL | DIR | INV | EN |

| Read  |    | Trig En (0 – 7) |    |    |    |    |   |   |   | Presc | aler |   | SEL | DIR | INV | EN |

|       |    |                 |    |    |    |    |   |   |   |       |      |   |     |     |     |    |

| 46    |    |                  |    |    |    |    |    |    |                |                  |    |    |    |    |    |    |

|-------|----|------------------|----|----|----|----|----|----|----------------|------------------|----|----|----|----|----|----|

| Bit   | 31 | 30               | 29 | 28 | 27 | 26 | 25 | 24 | 23             | 22               | 21 | 20 | 19 | 18 | 17 | 16 |

| Write |    | Trig Dir $(0-7)$ |    |    |    |    |    |    |                | Trig Inv $(0-7)$ |    |    |    |    |    |    |

| Read  |    | Trig Dir (0 – 7) |    |    |    |    |    |    | Trig Inv (0-7) |                  |    |    |    |    |    |    |

Trig En (0-7)  $\Rightarrow$  Trigger Bus Enable (1 = enable trigger line, all enabled input triggers are logically OR'ed, default = 0)

Prescaler  $\Rightarrow$  Prescaler Select (Selected clock is divided by this prescaler)

- $0 \ 0 \ 0$  Prescaler = 1 (default)

- $0 \ 0 \ 1$  Prescaler = 2

- $0 \ 1 \ 0$  Prescaler = 5

- 0 1 1 Prescaler = 10

- 1 0 0 Prescaler = 20

- 1 0 1 Prescaler = 50

- 1 1 0 Prescaler = 100

- 1 1 1 Prescaler = 200

- SEL ⇒ Trigger Select

- 0 0None(default)0 1Bussed TriggersIn/Out

- 1 0 Star Triggers In only

- 1 1 10 MHz In only

- DIR  $\Rightarrow$  Strobe Direction (0 = strobe input to IP, 1 = strobe output from IP, default = 0)

- INV  $\Rightarrow$  Strobe Invert (1 = inverted, default = 0)

- EN  $\Rightarrow$  Strobe Enable (1 = trigger enabled, default = 0)

- Trig Dir (0-7)  $\Rightarrow$  Trigger Bus Direction (0 = trigger input to PX403S, 1 = trigger output from PX403S)

- Trig Inv (0-7)  $\Rightarrow$  Trigger Bus Invert (1 = Inverted, default = 0)

Figure 6. IP Trigger Control Register

# 4.3 IP I/O OPERATIONS

The IP's I/O Space and ID PROM areas are accessed as an offset from BAR0. If the IP has on-board memory and the IP memory enable switch is ON, then the IP memory is accessed as an offset from BAR1.

During write transactions, the PX403S issues an auto acknowledge and completes the PCI cycle before the IP issues an acknowledge. For this reason, it is not possible to detect real-time IP write transaction errors. The PX403S does; however, have a timeout timer that prevents the interface from getting into a "hung" state. The PX403S also prevents missing bus transactions, by forcing the host to issue retries until the IP is ready for another transaction. The write cycle time is dependent on the speed of the IP and the number of wait states that are inserted.

During read transactions, the PX403S issues retries until the IP returns a data acknowledge. It then issues a "disconnect with data". If the IP does not acknowledge the cycle, the bus timeout timer will expire and a "target abort" will be issued. The data access cycle time is dependent on the speed of the IP and the number of wait states inserted.

The bus timeout timer is programmable and has several time options available to suit the transaction time required by the IP. The purpose of the timeout timer is to keep the interface from getting into a "hung" state when the IP does not issue an acknowledge. The timer can be programmed to expire from selected times ranging from 3.2 us to 3.2 s.

### 4.3.1 ID PROM Access

The IP ID PROM data ( $00_{16}$  to  $3E_{16}$ ) is mapped to PCI address apace BAR0+100<sub>16</sub> to BAR0+17F<sub>16</sub>. The format of ID PROM data can be either Type I or Type II. Consult the IP's documentation for details. If the format is Type I, only the lower (odd) byte is valid. The high byte is always FF<sub>16</sub>.

| PCI Address, hex  | Register Description              |  |  |  |  |

|-------------------|-----------------------------------|--|--|--|--|

| BAR0 + 100        | ASCII "I"                         |  |  |  |  |

| BAR0 + 104        | ASCII "P"                         |  |  |  |  |

| BAR0 + 108        | ASCII "A"                         |  |  |  |  |

| BAR0 + 10C        | ASCII "C" or "H"                  |  |  |  |  |

| BAR0 + 110        | Manufacturer ID                   |  |  |  |  |

| BAR0 + 114        | Model Number                      |  |  |  |  |

| BAR0 + 118        | Revision Level                    |  |  |  |  |

| BAR0 + 11C        | Reserved                          |  |  |  |  |

| BAR0 + 120        | Low Byte Driver ID (Firmware Rev) |  |  |  |  |

| BAR0 + 124        | High Byte Driver ID               |  |  |  |  |

| BAR0 + 12C        | Number of Bytes Used              |  |  |  |  |

| BAR0 + 130        | CRC                               |  |  |  |  |

| BAR0 + 134 to 17C | IP Module Specific & User Space   |  |  |  |  |

Table I. ID PROM Contents (Format I)

#### 4.3.2 I/O Space Access

The IP I/O Space  $(00_{16} \text{ to } 7E_{16})$  is mapped to PCI address space BAR0+ $00_{16}$  to BAR0+FC<sub>16</sub>. Since IPs use 16-bit addressing and PCI use 32-bit addressing, the IP address must be multiplied by two for the correct PCI address. When doing 32-bit PCI accesses, only the lower 16-bits are used.

#### 4.3.3 Memory Access

If the installed IP supports on-board memory and IP memory is enabled on the PX403S, the IP Memory Space  $(000000_{16} \text{ to } 3\text{FFFE}_{16})$  is mapped to PCI address space BAR1+000000\_{16} to BAR0+7FFFC\_{16}. Since IPs use 16-bit addressing and PCI use 32-bit addressing, the IP address must be multiplied by two for the correct PCI address. When doing 32-bit PCI accesses, only the lower 16-bits are used.

### 4.2.4 Interrupts

Each IP can support up to two interrupt requests as specified in the IndustryPack Logic Interface Specification. The interrupt scheme for each PCI interface follows the interrupt binding as recommended by the PCI and CPCI bus specifications. It is up to the Interrupt Service Routine (ISR) to determine the priority of multiple interrupts.

When an IP request an interrupt, a PCI interrupt is requested from the host. The PCI interrupt is cleared by removing the interrupt request from the IP or by writing a 1 to Bit 15 of the IP Status/Control Register (IP CNTL) in the PCI Configuration Space ( $40_{16}$ ). See Figure 5 for details. Writing to the IP CNTL Register clears the PCI interrupt, but not the IP interrupt. The ISR must handle the IP interrupt according to the IP's documentation.

Since PCI does not use interrupt vectors, the IP interrupt vectors (INTOVEC and INT1VEC) may be read at BAR0+180<sub>16</sub> and BAR0+184<sub>16</sub>, respectively, when and only when, the appropriate interrupt request from the IP is pending. If the register is read when an interrupt is not pending, a "target abort" is issued and the value read is  $FFFF_{16}$ .

### 4.2.5 Triggers

NOTE: Trigger signals are only supported in PXI systems or custom configured CPCI systems.

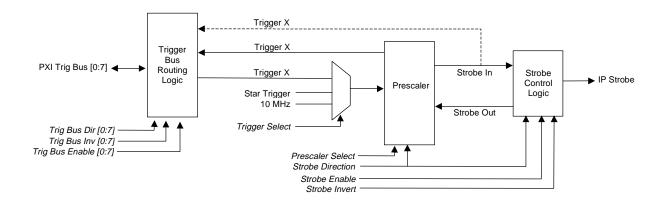

The PX403S supports PXI bus triggers, the STAR Trigger line and the 10 MHz system reference clock. The trigger logic is configured using the IP Trigger Control Register in the PCI Configuration Space  $(44_{16})$ . See Figure 6 for details.

The trigger logic also provides logical OR'ing and prescaler operations. All enabled PXI input triggers are logically OR'ed before the signal goes to the prescaler. All enabled output triggers reflect the same

output Strobe signal. The prescaler works for both input and output Strobes. The direction is determined by the Strobe Direction control bit. See Figure 7 for details.

The PX403S uses active driver logic (not open-collector) to output the PXI trigger signal to the backplane. Care must be taken to insure that multiple devices are not driving the same trigger line at the same time.

**Figure 7. Trigger Functional Diagram**

# **APPENDIX A - CONNECTORS**

| IP                                                                                                                                                                                                                                                                                                                                                         | А                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| I/O 50                                                                                                                                                                                                                                                                                                                                                     | I/O 25                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

| I/O 49                                                                                                                                                                                                                                                                                                                                                     | I/O 24                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

| I/O 48                                                                                                                                                                                                                                                                                                                                                     | I/O 23                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

| I/O 40                                                                                                                                                                                                                                                                                                                                                     | I/O 23                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

| I/O 46                                                                                                                                                                                                                                                                                                                                                     | I/O 21                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

| I/O 40                                                                                                                                                                                                                                                                                                                                                     | I/O 20                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

| I/O 43                                                                                                                                                                                                                                                                                                                                                     | I/O 19                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

| I/O 43                                                                                                                                                                                                                                                                                                                                                     | I/O 18                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

| I/O 43                                                                                                                                                                                                                                                                                                                                                     | I/O 10                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

| I/O 42                                                                                                                                                                                                                                                                                                                                                     | I/O 16                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

| I/O 41                                                                                                                                                                                                                                                                                                                                                     | I/O 10                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

| I/O 39                                                                                                                                                                                                                                                                                                                                                     | I/O 13                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

| I/O 38                                                                                                                                                                                                                                                                                                                                                     | I/O 14                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

| I/O 37                                                                                                                                                                                                                                                                                                                                                     | I/O 13                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                            | I/O 12<br>I/O 11                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| I/O 36<br>I/O 35                                                                                                                                                                                                                                                                                                                                           | I/O 10                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

| I/O 35                                                                                                                                                                                                                                                                                                                                                     | I/O 10                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                            | I/O 9<br>I/O 8                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |

| I/O 33<br>I/O 32                                                                                                                                                                                                                                                                                                                                           | I/O 8                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| I/O 32                                                                                                                                                                                                                                                                                                                                                     | I/O 7<br>I/O 6                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| I/O 30                                                                                                                                                                                                                                                                                                                                                     | I/O 5                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| I/O 29<br>I/O 28                                                                                                                                                                                                                                                                                                                                           | I/O 4<br>I/O 3                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| I/O 27                                                                                                                                                                                                                                                                                                                                                     | I/O 2                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| I/O 26                                                                                                                                                                                                                                                                                                                                                     | I/O 1                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| IP                                                                                                                                                                                                                                                                                                                                                         | В                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                            | B                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| I/O 50                                                                                                                                                                                                                                                                                                                                                     | I/O 25                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

| I/O 50<br>I/O 49                                                                                                                                                                                                                                                                                                                                           | I/O 25<br>I/O 24                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| I/O 50<br>I/O 49<br>I/O 48                                                                                                                                                                                                                                                                                                                                 | I/O 25<br>I/O 24<br>I/O 23                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| I/O 50<br>I/O 49<br>I/O 48<br>I/O 47                                                                                                                                                                                                                                                                                                                       | I/O 25<br>I/O 24<br>I/O 23<br>I/O 22                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| I/O 50<br>I/O 49<br>I/O 48<br>I/O 47<br>I/O 46                                                                                                                                                                                                                                                                                                             | I/O 25<br>I/O 24<br>I/O 23<br>I/O 22<br>I/O 21                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |

| I/O 50<br>I/O 49<br>I/O 48<br>I/O 47<br>I/O 46<br>I/O 45                                                                                                                                                                                                                                                                                                   | I/O 25<br>I/O 24<br>I/O 23<br>I/O 22<br>I/O 21<br>I/O 20                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| /O 50<br> /O 49<br> /O 48<br> /O 47<br> /O 46<br> /O 45<br> /O 44                                                                                                                                                                                                                                                                                          | I/O 25<br>I/O 24<br>I/O 23<br>I/O 22<br>I/O 21<br>I/O 20<br>I/O 19                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |

| I/O 50<br>I/O 49<br>I/O 48<br>I/O 47<br>I/O 46<br>I/O 45<br>I/O 44<br>I/O 43                                                                                                                                                                                                                                                                               | I/O 25<br>I/O 24<br>I/O 23<br>I/O 22<br>I/O 21<br>I/O 20<br>I/O 19<br>I/O 18                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

| I/O 50           I/O 49           I/O 48           I/O 47           I/O 46           I/O 45           I/O 43           I/O 43                                                                                                                                                                                                                              | I/O 25<br>I/O 24<br>I/O 23<br>I/O 22<br>I/O 21<br>I/O 20<br>I/O 19<br>I/O 18<br>I/O 17                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

| I/O 50           I/O 49           I/O 48           I/O 47           I/O 46           I/O 45           I/O 44           I/O 43           I/O 42           I/O 41                                                                                                                                                                                            | I/O 25           I/O 24           I/O 23           I/O 22           I/O 21           I/O 20           I/O 19           I/O 18           I/O 17           I/O 16                                                                                                                                                                                      |  |  |  |  |  |  |  |

| I/O 50           I/O 49           I/O 48           I/O 47           I/O 46           I/O 45           I/O 44           I/O 43           I/O 42           I/O 41           I/O 40                                                                                                                                                                           | I/O 25           I/O 24           I/O 23           I/O 22           I/O 21           I/O 20           I/O 19           I/O 18           I/O 17           I/O 16           I/O 15                                                                                                                                                                     |  |  |  |  |  |  |  |

| I/O 50           I/O 49           I/O 48           I/O 47           I/O 46           I/O 45           I/O 43           I/O 43           I/O 42           I/O 41           I/O 40                                                                                                                                                                           | I/O 25           I/O 24           I/O 23           I/O 22           I/O 21           I/O 20           I/O 19           I/O 18           I/O 17           I/O 16           I/O 15           I/O 14                                                                                                                                                    |  |  |  |  |  |  |  |

| I/O 50           I/O 49           I/O 48           I/O 47           I/O 46           I/O 45           I/O 43           I/O 42           I/O 41           I/O 40           I/O 39           I/O 38                                                                                                                                                          | I/O 25           I/O 24           I/O 23           I/O 22           I/O 21           I/O 20           I/O 19           I/O 17           I/O 16           I/O 15           I/O 13                                                                                                                                                                     |  |  |  |  |  |  |  |

| I/O 50           I/O 49           I/O 48           I/O 47           I/O 46           I/O 45           I/O 44           I/O 43           I/O 42           I/O 41           I/O 40           I/O 39           I/O 37                                                                                                                                         | I/O 25           I/O 24           I/O 23           I/O 22           I/O 21           I/O 20           I/O 19           I/O 18           I/O 17           I/O 16           I/O 15           I/O 13           I/O 12                                                                                                                                   |  |  |  |  |  |  |  |

| I/O 50           I/O 49           I/O 48           I/O 47           I/O 46           I/O 45           I/O 43           I/O 43           I/O 42           I/O 41           I/O 40           I/O 39           I/O 37           I/O 36                                                                                                                        | I/O 25           I/O 24           I/O 23           I/O 22           I/O 21           I/O 20           I/O 19           I/O 17           I/O 16           I/O 15           I/O 13           I/O 12           I/O 11                                                                                                                                   |  |  |  |  |  |  |  |

| I/O 50           I/O 49           I/O 48           I/O 47           I/O 46           I/O 45           I/O 43           I/O 43           I/O 42           I/O 41           I/O 40           I/O 39           I/O 36           I/O 35                                                                                                                        | I/O 25           I/O 24           I/O 23           I/O 22           I/O 21           I/O 20           I/O 19           I/O 18           I/O 17           I/O 16           I/O 15           I/O 13           I/O 12           I/O 10                                                                                                                  |  |  |  |  |  |  |  |

| I/O 50           I/O 49           I/O 48           I/O 47           I/O 45           I/O 45           I/O 44           I/O 43           I/O 42           I/O 41           I/O 40           I/O 39           I/O 36           I/O 35           I/O 34                                                                                                       | I/O 25           I/O 24           I/O 23           I/O 21           I/O 21           I/O 20           I/O 19           I/O 18           I/O 17           I/O 16           I/O 15           I/O 13           I/O 12           I/O 10           I/O 9                                                                                                  |  |  |  |  |  |  |  |

| I/O 50           I/O 49           I/O 48           I/O 47           I/O 46           I/O 45           I/O 43           I/O 42           I/O 41           I/O 40           I/O 43           I/O 43           I/O 40           I/O 39           I/O 38           I/O 36           I/O 35           I/O 33                                                    | I/O 25           I/O 24           I/O 23           I/O 21           I/O 20           I/O 19           I/O 18           I/O 17           I/O 16           I/O 15           I/O 13           I/O 12           I/O 10           I/O 9           I/O 8                                                                                                   |  |  |  |  |  |  |  |

| I/O 50           I/O 49           I/O 48           I/O 47           I/O 45           I/O 45           I/O 44           I/O 43           I/O 42           I/O 41           I/O 40           I/O 39           I/O 36           I/O 35           I/O 33           I/O 32                                                                                      | I/O 25           I/O 24           I/O 23           I/O 22           I/O 21           I/O 20           I/O 19           I/O 18           I/O 17           I/O 16           I/O 15           I/O 14           I/O 13           I/O 12           I/O 10           I/O 9           I/O 8           I/O 7                                                 |  |  |  |  |  |  |  |

| I/O 50           I/O 49           I/O 48           I/O 47           I/O 46           I/O 45           I/O 44           I/O 43           I/O 42           I/O 41           I/O 40           I/O 39           I/O 36           I/O 35           I/O 33           I/O 32           I/O 31                                                                     | I/O 25           I/O 24           I/O 23           I/O 22           I/O 21           I/O 20           I/O 19           I/O 18           I/O 17           I/O 16           I/O 15           I/O 13           I/O 12           I/O 10           I/O 9           I/O 8           I/O 7           I/O 6                                                  |  |  |  |  |  |  |  |

| I/O 50           I/O 49           I/O 48           I/O 47           I/O 45           I/O 45           I/O 44           I/O 43           I/O 42           I/O 41           I/O 40           I/O 39           I/O 36           I/O 35           I/O 32           I/O 31           I/O 30                                                                     | I/O 25           I/O 24           I/O 23           I/O 22           I/O 10           I/O 19           I/O 18           I/O 17           I/O 16           I/O 15           I/O 13           I/O 12           I/O 10           I/O 9           I/O 8           I/O 7           I/O 6           I/O 5                                                   |  |  |  |  |  |  |  |

| I/O 50           I/O 49           I/O 48           I/O 47           I/O 46           I/O 45           I/O 43           I/O 43           I/O 42           I/O 41           I/O 40           I/O 39           I/O 38           I/O 36           I/O 35           I/O 33           I/O 32           I/O 30           I/O 30                                   | I/O 25           I/O 24           I/O 23           I/O 22           I/O 21           I/O 20           I/O 19           I/O 18           I/O 17           I/O 16           I/O 15           I/O 14           I/O 13           I/O 12           I/O 10           I/O 9           I/O 8           I/O 7           I/O 6           I/O 5           I/O 4 |  |  |  |  |  |  |  |

| I/O 50           I/O 49           I/O 48           I/O 47           I/O 45           I/O 45           I/O 44           I/O 45           I/O 44           I/O 43           I/O 41           I/O 40           I/O 39           I/O 36           I/O 35           I/O 33           I/O 32           I/O 31           I/O 30           I/O 29           I/O 28 | I/O 25         I/O 24         I/O 23         I/O 22         I/O 10         I/O 19         I/O 18         I/O 17         I/O 16         I/O 15         I/O 14         I/O 13         I/O 12         I/O 10         I/O 9         I/O 8         I/O 7         I/O 6         I/O 5         I/O 4                                                        |  |  |  |  |  |  |  |

| I/O 50           I/O 49           I/O 48           I/O 47           I/O 46           I/O 45           I/O 43           I/O 43           I/O 42           I/O 41           I/O 40           I/O 39           I/O 38           I/O 36           I/O 35           I/O 33           I/O 32           I/O 30           I/O 30                                   | I/O 25           I/O 24           I/O 23           I/O 22           I/O 21           I/O 20           I/O 19           I/O 18           I/O 17           I/O 16           I/O 15           I/O 14           I/O 13           I/O 12           I/O 10           I/O 9           I/O 8           I/O 7           I/O 6           I/O 5           I/O 4 |  |  |  |  |  |  |  |

(As viewed towards front panel)

# Front Panel I/O Connector Pin Configuration

| I/O Pin | Signal | [ | I/O Pin | Signal   |

|---------|--------|---|---------|----------|

| 1       | GND    |   | 26      | GND      |

| 2       | CLK    |   | 27      | +5V      |

| 3       | RESET- |   | 28      | R/W-     |

| 4       | D0     |   | 29      | IDSEL-   |

| 5       | D1     |   | 30      | DMAREQ0- |

| 6       | D2     |   | 31      | MEMSEL-  |

| 7       | D3     |   | 32      | DMAREQ1- |

| 8       | D4     |   | 33      | INTSEL-  |

| 9       | D5     |   | 34      | DMACK0-  |

| 10      | D6     |   | 35      | IOSEL-   |

| 11      | D7     |   | 36      | reserved |

| 12      | D8     |   | 37      | A1       |

| 13      | D9     |   | 38      | DMAEND-  |

| 14      | D10    |   | 39      | A2       |

| 15      | D11    |   | 40      | ERROR-   |

| 16      | D12    |   | 41      | A3       |

| 17      | D13    |   | 42      | INTREQ0- |

| 18      | D14    |   | 43      | A4       |

| 19      | D15    |   | 44      | INTREQ1- |

| 20      | BS0-   |   | 45      | A5       |

| 21      | BS1-   |   | 46      | STROBE-  |

| 22      | -12V   |   | 47      | A6       |

| 23      | +12V   |   | 48      | ACK-     |

| 24      | +5V    |   | 49      | reserved |

| 25      | GND    |   | 50      | GND      |

# **IP Interface Pin Configuration**

| PIN | Z   | А        | В        | С        | D      | E        | F   |

|-----|-----|----------|----------|----------|--------|----------|-----|

| 1   | GND | 5V       | -12V     | TRST#    | +12V   | 5V       | GND |

| 2   | GND | TCK      | 5V       | TMS      | TDO    | TDI      | GND |

| 3   | GND | INTA#    | INTB#    | INTC#    | 5V     | INTD#    | GND |

| 4   | GND | BRSVP1A4 | GND      | V(I/O)   | INTP   | INTS     | GND |

| 5   | GND | BRSVP1A5 | BRSVP1B5 | RST#     | GND    | GNT#     | GND |

| 6   | GND | REQ#     | GND      | 3.3V     | CLK    | AD[31]   | GND |

| 7   | GND | AD[30]   | AD[29]   | AD[28]   | GND    | AD[27]   | GND |

| 8   | GND | AD[26]   | GND      | V(I/O)   | AD[25] | AD[24]   | GND |

| 9   | GND | C/BE[3]# | IDSEL    | AD[23]   | GND    | AD[22]   | GND |

| 10  | GND | AD[21]   | GND      | 3.3V     | AD[20] | AD[19]   | GND |

| 11  | GND | AD[18]   | AD[17]   | AD[16]   | GND    | C/BE[2]# | GND |

| 12  |     |          |          |          |        |          |     |

| 13  |     |          |          | Key Area |        |          |     |

| 14  |     |          |          | -        |        |          |     |

| 15  | GND | 3.3V     | FRAME#   | IRDY#    | GND    | TRDY#    | GND |

| 16  | GND | DEVSEL#  | GND      | V(I/O)   | STOP#  | LOCK#    | GND |

| 17  | GND | 3.3V     | SDONE    | SBO#     | GND    | PERR#    | GND |

| 18  | GND | SERR#    | GND      | 3.3V     | PAR    | C/BE[1]  | GND |

| 19  | GND | 3.3V     | AD[15]   | AD[14]   | GND    | AD[13]   | GND |

| 20  | GND | AD[12]   | GND      | V(I/O)   | AD[11] | AD[10]   | GND |

| 21  | GND | 3.3V     | AD[9]    | AD[8]    | M66EN  | C/BE[0]# | GND |

| 22  | GND | AD[7]    | GND      | 3.3V     | AD[6]  | AD[5]    | GND |

| 23  | GND | 3.3V     | AD[4]    | AD[3]    | 5V     | AD[2]    | GND |

| 24  | GND | AD[1]    | 5V       | V(I/O)   | AD[0]  | ACK64#   | GND |

| 25  | GND | 5V       | REQ64#   | ENUM#    | 3.3V   | 5V       | GND |

# **PXI/CPCI J1 Pin Configuration**

| PIN | Z   | A           | В          | С          | D          | E          | F   |

|-----|-----|-------------|------------|------------|------------|------------|-----|

| 1   | GND | PXI LBL9    | GND        | PXI LBL10  | PXI LBL11  | PXI LBL12  | GND |

| 2   | GND | PXI_LBR11   | PXI_LBR12  | SYSEN#     | PXI_LBL7   | PXI_LBL8   | GND |

| 3   | GND | PXI_LBR7    | GND        | PXI_LBR8   | PXI_LBR9   | PXI_LBR10  | GND |

| 4   | GND | V(I/O)      | PXI_RSVB4  | C/BE[7]#   | GND        | C/BE[6]#   | GND |

| 5   | GND | C/BE[5]#    | GND        | V(I/O)     | C/BE[4]#   | PAR64      | GND |

| 6   | GND | AD[63]      | AD[62]     | AD[61]     | GND        | AD[60]     | GND |

| 7   | GND | AD[59]      | GND        | V(I/O)     | AD[58]     | AD[57]     | GND |

| 8   | GND | AD[56]      | AD[55]     | AD[54]     | GND        | AD[53]     | GND |

| 9   | GND | AD[52]      | GND        | V(I/O)     | AD[51]     | AD[50]     | GND |

| 10  | GND | AD[49]      | AD[48]     | AD[47]     | GND        | AD[46]     | GND |

| 11  | GND | AD[45]      | GND        | V(I/O)     | AD[44]     | AD[43]     | GND |

| 12  | GND | AD[42]      | AD[41]     | AD[40]     | GND        | AD[39]     | GND |

| 13  | GND | AD[38]      | GND        | V(I/O)     | AD[37]     | AD[36]     | GND |

| 14  | GND | AD[35]      | AD[34]     | AD[33]     | GND        | AD[32]     | GND |

| 15  | GND | PXI_BRSVA15 | GND        | FAL#       | PXI_LBL6   | PXI_LBR6   | GND |

| 16  | GND | PXI_TRIG1   | PXI_TRIG0  | DEG#       | GND        | PXI_TRIG7  | GND |

| 17  | GND | PXI_TRIG2   | GND        | PRST#      | PXI_STAR   | PXI_CLK10  | GND |

| 18  | GND | PXI_TRIG3   | PXI_TRIG4  | PXI_TRIG5  | GND        | PXI_TRIG6  | GND |

| 19  | GND | PXI_LBL2    | GND        | PXI_LBL3   | PXI_LBL4   | PXI_LBL5   | GND |

| 20  | GND | PXI_LBR4    | PXI_LBR5   | PXI_LBL0   | GND        | PXI_LBL1   | GND |

| 21  | GND | PXI_LBR0    | GND        | PXI_LBR1   | PXI_LBR2   | PXI_LBR3   | GND |

| 22  | GND | PXI_RSVA22  | PXI_RSVB22 | PXI_RSVC22 | PXI_RSVD22 | PXI_RSVE22 | GND |

# **PXI/CPCI J2** Pin Configuration

NOTES: Bold-faced words are PXI defined signals. Italicized words are unused signals. Underlined words are used by the system slot.

#### **APPENDIX B - PCI CONFIGURATION REGISTERS**

The configuration registers contain basic information needed to configure a PXI/CPCI system. **This information is provided for reference only.** For complete information, please refer to the latest PCI Specification.

| A16 Address | Register Description        |

|-------------|-----------------------------|

| Base + 00   | Vendor ID*                  |

| Base + 02   | Device ID*                  |

| Base $+ 04$ | Command*                    |

| Base + 06   | Status*                     |

| Base + 08   | Revision ID                 |

| Base + 09   | Class Code                  |

| Base + 0C   | Cache Line Size             |

| Base + 0D   | Latency Timer               |

| Base + 0E   | Header Type                 |

| Base + 0F   | BIST                        |

| Base + 10   | Base Address Registers*     |

| Base + 28   | Cardbus CIS Pointer         |

| Base + 2C   | Subsystem Vendor ID         |

| Base + 2E   | Subsystem ID                |

| Base $+30$  | Expansion ROM Based Address |

| Base + 34   | CAP_PTR                     |

| Base + 35   | Reserved                    |

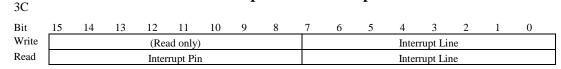

| Base + 3C   | Interrupt Line*             |

| Base + 3D   | Interrupt Pin*              |

| Base + 3E   | Min_Gnt                     |

| Base + 3F   | Max_Lat                     |

#### **IP** Configuration Registers

\* Bit details provided below.

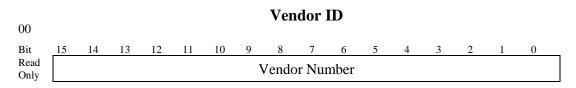

<u>Vendor (ID) Register</u> (Base  $+ 00_{16}$ ) This read-only register provides vendor identification and is assigned by the PCI Special Interest Group.

<u>Device (ID) Register</u> (Base  $+ 02_{16}$ ) This read-only register provides the vendor identifier. The vendor ID is assigned by the vendor.

<u>Command Register</u> (Base  $+ 04_{16}$ ) This read/write register is used to control the devices ability to respond to bus accesses.

<u>Status Register</u> (Base + 06<sub>16</sub>) This read-only register is used by the device to record any catastrophic event that might interrupt normal operation.

<u>Revision (ID) Register</u> (Base  $+ 08_{16}$ ) This read-only register is supplied by the vendor in order to indicate the revision level of the device.

<u>Class Code Register</u> (Base  $+ 09_{16}$ ) This read-only register provides information concerning the generic function of the device.

<u>Cache Line Size Register</u> (Base  $+ 0C_{16}$ ) This read-only register provides information on the cacheline length. This register is used during bursting. This register is not used in this application and should be ignored.

<u>Latency Timer Register</u> (Base + 0D<sub>16</sub>) This read/write register is used to define the maximum amount of time that a device can control the bus in times of heavy traffic.

<u>Header Type Register</u> (Base  $+ 0E_{16}$ ) This read-only register provides information concerning the header type of the device. This also specifies whether the device is multifunctional or not. For our application the header type that we will use is 00H.

<u>PXI BIST Register</u> (Base + 0F<sub>16</sub>) This read/write register invokes and reports the results of the built in self-test. If the device does not support this function, then a 00H must be returned.