USER'S MANUAL

# HIGH SPEED APERTURE A/D M-MODULE

MODEL M228

### COPYRIGHT

C&H Technologies, Inc. (C&H) provides this manual "as is" without warranty of any kind, either expressed or implied, including but not limited to the implied warranties of merchantability and fitness for a particular purpose. C&H may make improvements and/or changes in the product(s) and/or program(s) described in this manual at any time and without notice.

This publication could contain technical inaccuracies or typographical errors. Changes are periodically made to the information herein; these changes will be incorporated in new editions of this publication.

### Copyright © 2009 by C&H Technologies, Inc.

The information and/or drawings set forth in this document and all rights in and to inventions disclosed herein which might be granted thereon disclosing or employing the materials, methods, techniques, or apparatus described herein, are the exclusive property of C&H Technologies, Inc.

A Reader's Comment Form is provided at the back of this publication. If this form has been removed address comments to:

C&H Technologies, Inc. Technical Publications 445 Round Rock West Drive Austin, Texas 78681-5012

Or visit our web site for support information at:

http://www.chtech.com.

C&H may use or distribute any of the information you supply in any way that it believes appropriate without incurring any obligations.

# **AMENDMENT NOTICE**

C&H Technologies, Inc. makes every attempt to provide up-to-date manuals with the associated equipment. Occasionally, changes are made to the equipment wherein it is necessary to provide amendments to the manual. If any amendments are provided for this manual they are printed on colored paper and will be provided with the module and manual. Manual updates may also be found on out web site at www.chtech.com.

### NOTE

The contents of any amendment may affect operation, maintenance, or calibration of the equipment.

# **INTRODUCTION**

This manual describes the operation and use of the C&H Model M228 High Speed Aperture A/D (Part Number 11030500). This mezzanine module is designed to interface within any M/MA-Module carrier adhering to the ANSI/VITA 12-1996 M-Module specification. These carriers are available in many formats such as VME, VXI, LXI, PXI, cPCI, and the PC.

Contained within this manual are the physical and electrical specifications, installation and startup procedures, functional description, and configuration and programming guidelines to adequately use the product.

This manual is based on a low level register access, and is written in such a manner to provide understanding to the user based on this type of access. If a driver is provided, please refer to the driver documentation for instruction using the higher level interface provided by the driver.

# TABLE OF CONTENTS

| 1.0 GENERAL DES  | CRIPTION                          | 1    |

|------------------|-----------------------------------|------|

| 1.1 PURPOSE      | E OF EQUIPMENT                    | 1    |

| 1.2 SPECIFIC     | CATIONS OF EQUIPMENT              | 1    |

| 1.2.1            | Key Features                      |      |

| 1.2.2            | Specifications                    | 2    |

| 1.2.3            | Mechanical                        | 6    |

| 1.2.4            | Bus Compliance                    | 6    |

| 1.2.5            | Applicable Documents              | 6    |

| 1.2.6            | Credits                           | 6    |

| 2.0 INSTALLATION | N                                 | 7    |

| 2.1 UNPACK       | ING AND INSPECTION                | 7    |

| 2.2 HANDLIN      | NG PRECAUTIONS                    | 7    |

| 2.3 INSTALL      | ATION OF M MODULES                | 7    |

| 2.4 PREPARA      | ATION FOR RESHIPMENT              | 8    |

| 3.0 FUNCTIONAL I | DESCRIPTION                       | 9    |

| 3.1 OVERVIE      | EW                                | 9    |

| 3.1.1            | Programmable Divider              | 9    |

| 3.1.2            | Self test and Calibration Logic   | 9    |

| 3.1.3            | References                        |      |

| 3.1.4            | Instrumentation Amplifier (IA)    | 9    |

| 3.1.5            | Anti-Aliasing Filter              | . 10 |

| 3.1.6            | Programmable Gain Amplifier (PGA) |      |

| 3.1.7            | Analog Digital Converter (ADC)    | . 10 |

| 3.1.8            | Aperture Comparator               |      |

| 3.1.9            | FIFO                              | . 10 |

| 3.1.10           | 32-Bit Timestamp                  | . 11 |

| 3.1.11           | Clock/Run Control                 | . 11 |

| 3.1.12           | On-board Oscillator               | . 11 |

| 3.1.13           | External Inputs and Control       | . 11 |

| 3.1.14           | External Outputs and Control      | . 11 |

| 3.1.15           | M-Triggers & Control              | . 11 |

| 3.1.16           | Calibration                       | . 12 |

| 3.2 INPUT/O      | UTPUT SIGNALS                     | . 12 |

| 3.3 CONFIGU      | JRATION AND IDENTIFICATION        | . 13 |

| 3.3.1            | Programming Registers             | . 13 |

| 3.3.2            | M-Module Identification PROM      | . 28 |

| 4.0 OPERATION    |                                   | . 29 |

| 4.1 A/D CON      | VERSION                           | . 29 |

| 4.2 VALUE-T      | TME PAIR STORAGE                  | . 29 |

| 4.3 APERTU       | RE WINDOWS                        | . 30 |

| 4.3.1            | Aperture Mode 0                   | . 30 |

| 4.3.2            | Aperture Mode 1                   | . 30 |

| 4.3.3            | Aperture Mode 2                   | . 31 |

| 4.3.4            | Aperture Mode 3                   | . 31 |

| 4.3.5 Aperture Mode 4 |  |

|-----------------------|--|

| 4.3.6 Aperture Mode 5 |  |

| 4.3.7 Aperture Mode 6 |  |

| 4.4 FILTER SELECTION  |  |

| 4.5 CALIBRATION       |  |

| 4.6 ID PROM           |  |

| LIST OF APPENDICES    |  |

| APPENDIX A: CONNECTORS   | 1 1 |

|--------------------------|-----|

| AT I ENDIA A. CONNECTORS | J-1 |

# LIST OF FIGURES

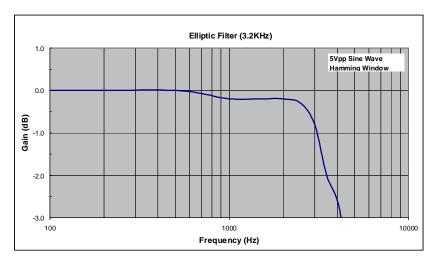

| Figure 1. Frequency Response - Elliptic Filter             | 4   |

|------------------------------------------------------------|-----|

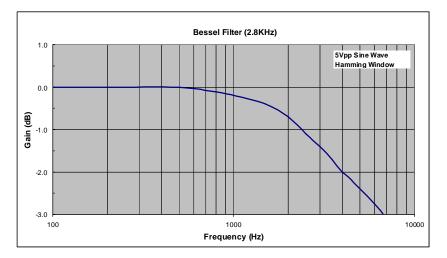

| Figure 2. Frequency Response - Bessel Filter               | 4   |

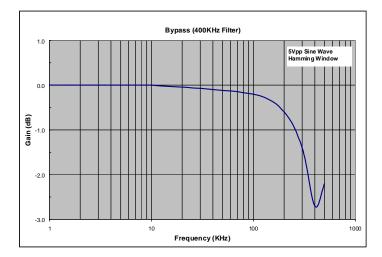

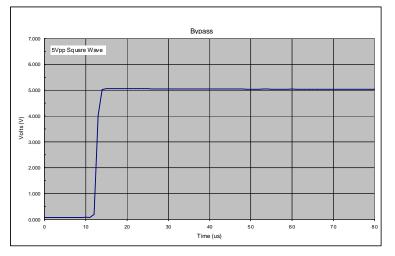

| Figure 3. Frequency Response - Bypass                      |     |

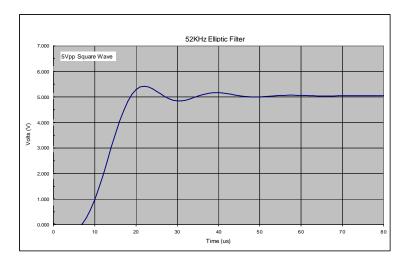

| Figure 4. Transient Response - Elliptic Filter             | 5   |

| Figure 5. Transient Response - Bessel Filter               | 5   |

| Figure 6. Transient Response - Bypass                      | 5   |

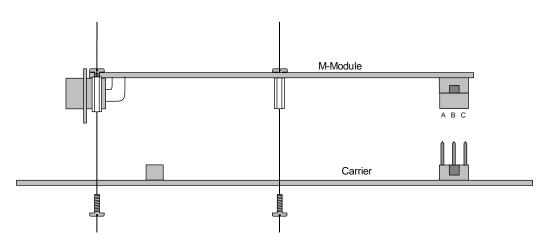

| Figure 7. M-Module Installation                            |     |

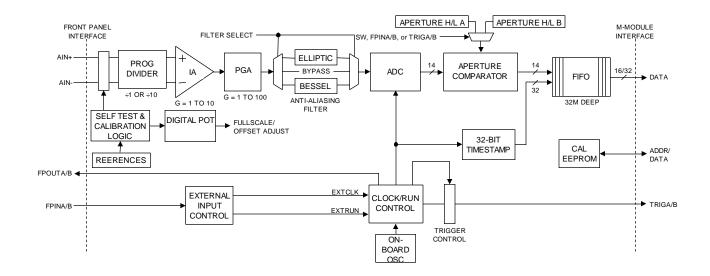

| Figure 8. Functional Block Diagram                         | 9   |

| Figure 9. Programming Registers                            | 14  |

| Figure 10. ID PROM Access Routine                          | 34  |

| -                                                          |     |

| Figure A-1. M/MA Interface Connector Configuration         | A-1 |

| Figure A-2. Front Panel Coax D-SUB Connector Configuration | A-2 |

# LIST OF TABLES

| Table I. Register Address Map             | 13 |

|-------------------------------------------|----|

| Table II. M-Module EEPROM IDENT Words     |    |

| Table III. EEPROM Calibration Data Format |    |

| Table IV. Single Calibration Entry Format |    |

|                                           |    |

# **1.0 GENERAL DESCRIPTION**

The M228 is a 1MSPS 14-bit A/D converter module that samples and selectively stores differential analog signals along with a 32-bit time stamp at a rate up to 1MSPS. The module has the ability to convert and store all data at the specified sample rate or selectively store input values that exceed the range of the programmed aperture window. This technique provides extensive real-time data compression and data extraction for transient type input signals

The module conforms to the ANSI/VITA 12-1996 standard for M-modules, which allows it to be used in a variety of platforms, including VXI, LXI, PXI, VME, PCI, cPCI, and Ethernet, with the use of an M-module carrier.

# 1.1 PURPOSE OF EQUIPMENT

This instrument is designed for data acquisition applications required in industrial test and measurement systems. The instrument allows high speed (1MSPS) data acquisition and analysis of transient analog signals without massive amounts of data being stored.

# **1.2 SPECIFICATIONS OF EQUIPMENT**

- 1.2.1 Key Features

- 14-Bit Resolution

- Up to 1MSPS

- Bipolar Differential Input

- 32-Bit Timestamp

- 32Meg Deep Sample FIFO in Value-Time Pair storage mode

- 64Meg Deep Sample FIFO in Value Only storage mode

- Flexible Real-time Data Storage Modes with external real-time change capability

- Capture Till Full and Continuous Capture Mode

- Continue Time-Stamping while Capture Disabled

- External "Data Stored" signal

- Two Programmable Anti-aliasing Filters (one Bessel response and the other a linear phase elliptic response) plus a bypass mode

- Programmable Gain (front-end 1, 2, 5, or 10 and back-end 1, 2. 5, 10, 20, 50, or 100)

- Programmable 10:1 Voltage Divider

- ±60V Input Range

- 10MΩ Input Impedance

# 1.2.2 Specifications

# MAXIMUM RATINGS

| Parameter                            | Condition                  | Rating               | Units |

|--------------------------------------|----------------------------|----------------------|-------|

| Operating Temperature                |                            | 0 to +50             | °C    |

| Non-Operating Temperature            |                            | -40 to +71           | °C    |

| Humidity                             | non-condensing             | 5 to 95              | %     |

| Power Consumption                    | +5V                        | 485 (typ), 500 (max) | mA    |

|                                      | +12V                       | 40 (typ), 100 (max)  | mA    |

|                                      | -12V                       | 80 (typ), 150 (max)  | mA    |

| Auxiliary Power Supply Current       | +5V                        | 500                  | mA    |

|                                      | +12V                       | 100                  | mA    |

|                                      | -12V                       | 100                  | mA    |

| Voltage on Analog Inputs (AIN0+/-)   | input connector limitation | ± 60                 | V     |

| Voltage on External Inputs (FPINA/B) | no damage, power off       | ± 40                 | V     |

|                                      | no damage, power on        | ± 36                 | V     |

SPECIFICATIONS (full operating temperature, unless otherwise specified)

| Parameter                    | Conditions                                                         |       | Units |      |       |

|------------------------------|--------------------------------------------------------------------|-------|-------|------|-------|

|                              |                                                                    | Min   | Тур   | Max  |       |

| A/D Converter                | -                                                                  |       | •     | •    |       |

| Resolution                   | no missing codes                                                   |       |       | 14   | bits  |

| Integral Linearity Error     |                                                                    | -1    | ±0.3  | +1   | LSB   |

| Differential Linearity Error |                                                                    | -1    |       | +1   | LSB   |

| Zero Error                   | before calibration                                                 | -15   |       | +15  | LSB   |

| Full Scale Error             | before calibration                                                 | -20   |       | +20  | LSB   |

| Zero Error Drift             |                                                                    |       |       | 0.1  | mV/°C |

| Full Scale Error Drift       |                                                                    |       |       | 0.1  | mV/°C |

| Throughput                   | Warp Mode <sup>1</sup>                                             | 0.001 |       | 1    | MSPS  |

|                              | Normal Mode                                                        | 0     |       | 800  | KSPS  |

| Signal to Noise Ratio        |                                                                    |       | 85.5  |      | dB    |

| Signal Input Conditioning    |                                                                    |       |       |      |       |

| Input Range                  | normal (G = 1)                                                     | -10   |       | +10  | V     |

|                              | $\div$ 10 active (G = 1)                                           | -60   |       | +60  | V     |

| Common Mode Voltage Range    |                                                                    | ±13   |       |      | V     |

| Common Mode Rejection Ratio  | dc to 50KHz                                                        | 80    |       |      | dB    |

| Input Impedance              | differential                                                       | 20    |       |      | MΩ    |

|                              | common-mode                                                        | 10    |       |      | MΩ    |

|                              | ÷10 active                                                         | 10    |       |      | MΩ    |

| Divider                      | programmable (1 or ÷10)                                            | 1     |       | 0.1  | V/V   |

| Gain                         | overall                                                            | 1     |       | 1000 | V/V   |

|                              | front end (1, 2, 5, or 10)                                         | 1     |       | 10   | V/V   |

|                              | back end (1, 2. 5, 10, 20, 50, or 100)                             | 1     |       | 100  | V/V   |

| Filter Cutoff Frequencies    | Elliptic, programmable in binary steps                             | 1.6   |       | 416  | KHz   |

|                              | Bessel, programmable in binary steps                               | 0.3   |       | 88   | KHz   |

| Filter Response              | See Frequency & Transient Response<br>Curves (Figure 1 - Figure 6) |       |       |      |       |

| Group Delay                  | Elliptic, $f_c = 104 KHz$                                          | 11.7  | 12    | 14.2 | μs    |

|                              | Bessel, f <sub>C</sub> = 88KHz                                     | 6     | 7     | 8    | μs    |

# SPECIFICATIONS (continued)

| Parameter                     | Conditions                       |                          | Limits     |       |        |  |

|-------------------------------|----------------------------------|--------------------------|------------|-------|--------|--|

|                               |                                  | Min                      | Тур        | Max   |        |  |

| Internal Sample Clock         |                                  |                          |            | •     |        |  |

| Accuracy                      |                                  |                          |            | ±0.01 | %      |  |

| Frequency                     | incremental (see note 3)         | 10Hz                     |            | 1     | MHz    |  |

| Jitter                        |                                  |                          |            | ±500  | ps     |  |

| Calibration References        |                                  |                          |            |       |        |  |

| Accuracy                      | ±0.5V                            | -0.35                    |            | 0.35  | %      |  |

|                               | ±10V                             | -0.1                     |            | 0.1   | %      |  |

| Temperature Coefficient       | ±0.5V                            |                          |            | 25    | ppm/°C |  |

|                               | ±10V                             |                          |            | 50    | ppm/°C |  |

| External Inputs (FPINA & FPIN | B)                               |                          |            | •     |        |  |

| Input Threshold               | programmable                     | 0                        |            | +5.0  | V      |  |

| Input Impedance               | programmable for $50\Omega$ or   | 45                       | 50         | 55    | Ω      |  |

|                               | Hi-Z                             | 19K                      |            |       | Ω      |  |

| Pulse Width                   |                                  | 5                        |            |       | ns     |  |

| Frequency                     | see note 4                       |                          |            | 50    | MHz    |  |

| External Outputs (FPOUTA & F  | POUTB)                           | 1                        |            |       | •      |  |

| Driver Type                   | Two 74ABT125 outputs in parallel | with a $25\Omega$ series | s resistor |       |        |  |

| Output High Voltage           | V <sub>OH</sub> at -6ma          | 2.5                      |            |       | V      |  |

|                               | V <sub>OH</sub> at -64ma         | 2.0                      |            |       | V      |  |

| Output Low Voltage            | V <sub>OL</sub> at 128ma         |                          |            | 0.55  | V      |  |

Specification Notes: 1. In Warp Mode, the time between conversions must not exceed 1ms.

2. 3. Relative to gain at  $0.1f_{c}$ . The internal clock rate is 1MHz. Sixteen programmable prescalers allow the internal sample rates to vary from 10Hz to 1MHz.

This is the maximum frequency that the input logic can accept. The maximum functional frequency is limited by the use of the input signal. 4.

Figure 1. Frequency Response - Elliptic Filter

Figure 2. Frequency Response - Bessel Filter

Figure 3. Frequency Response - Bypass

Figure 5. Transient Response - Bessel Filter

Figure 6. Transient Response - Bypass

# 1.2.3 Mechanical

The mechanical dimensions of the module are in conformance with ANSI/VITA 12-1996 for single-wide M-Module modules. The nominal dimensions are 5.687" (144.5 mm) long  $\times$  2.082" (106.2 mm) wide.

# 1.2.4 Bus Compliance

The module complies with the ANSI/VITA 12-1996 Specification for single-wide M-Modules. The module also supports the optional IDENT and VXI-IDENT functions.

| Module Type:     | M-Module                  |

|------------------|---------------------------|

| Addressing:      | A08                       |

| Data:            | D16, D32                  |

| Interrupts:      | INTC (ROAK with vector)   |

| Burst:           | not supported             |

| DMA:             | not supported             |

| Triggers:        | MTRGA & MTRGB             |

| Identification:  | IDENT and VXI-IDENT       |

| Manufacturer ID: | 0FC1 <sub>16</sub>        |

| Model Number:    | $00E4_{16}$ (228 dec.)    |

| VXI Model Code:  | 0FD4 <sub>16</sub> (M228) |

# 1.2.5 Applicable Documents

ANSI/VITA 12-1996 Standard for The Mezzanine Concept M-Module Specification, Approved May 20, 1997, American National Standards Institute and VMEbus International Trade Association, 7825 E. Gelding Dr. Suite 104, Scottsdale, AZ 85260-3415, <u>www.vita.com</u>

# 1.2.6 Credits

The following open source code was used in the design of this module:

- 1. I2CWB Wrapper (C) Victor Lopez Lorenzo under LGPL license

- 2. WISHBONE rev.B2 compliant synthesizable I2C Slave model (C) 2001 Richard Herveille <u>richard@asics.ws</u> under LGPL license

# 2.0 INSTALLATION

# 2.1 UNPACKING AND INSPECTION

Verify that there has been no damage to the shipping container. If damage exists then the container should be retained, as it will provide evidence of carrier caused problems. Such problems should be reported to the shipping courier immediately, as well as to C&H. If there is no damage to the shipping container, carefully remove the module from its box and anti static bag and inspect for any signs of physical damage. If damage exists, report immediately to C&H.

# 2.2 HANDLING PRECAUTIONS

The M228 contains components that are sensitive to electrostatic discharge. When handling the module for any reason, do so at a static-controlled workstation, whenever possible. At a minimum, avoid work areas that are potential static sources, such as carpeted areas. Avoid unnecessary contact with the components on the module.

# 2.3 INSTALLATION OF M MODULES

All M-Modules must be installed into the carrier before the carrier is installed into the host system. To install a module, firmly press the connector on the M-Module together with the connector on the carrier as shown in Figure 7. Secure the module through the holes in the bottom shield using the original screws.

CAUTION: M-Module connectors are NOT keyed. Use extra caution to avoid misalignment. Applying power to a misaligned module can damage the M-Module and carrier.

Figure 7. M-Module Installation

# 2.4 PREPARATION FOR RESHIPMENT

If the module is to be shipped separately it should be enclosed in a suitable water and vapor proof anti-static bag. Heat seal or tape the bag to insure a moisture-proof closure. When sealing the bag, keep trapped air volume to a minimum. The shipping container should be a rigid box of sufficient size and strength to protect the equipment from damage. If the module was received separately from a C&H system, then the original module shipping container and packing material may be re-used if it is still in good condition.

# **3.0 FUNCTIONAL DESCRIPTION**

# 3.1 OVERVIEW

A simplified functional block diagram of the module is shown in Figure 8.

# Figure 8. Functional Block Diagram

### 3.1.1 Programmable Divider

The programmable divider allows the input voltage to be divided by ten in order to handle input voltage levels up to 60V.

### 3.1.2 Self test and Calibration Logic

The self test and calibration logic can insert a reference signal at the inputs of the instrumentation amplifier. This reference signal can be used to self test or calibrate the unit.

3.1.3 References

Several references are provided to allow internal reference calibration and self-test.

3.1.4 Instrumentation Amplifier (IA)

The instrumentation amplifier provides differential input signal buffering and conditioning. This amplifier also provides a programmable (front end) gain of 1, 2, 5 or 10.

# 3.1.5 Anti-Aliasing Filter

Two types of anti-aliasing filters and bypass mode are provided. The elliptic filter is a 10th order low pass filter with a linear phase and a root raised cosine amplitude response. It has very steep roll-off and its cutoff frequency is programmable from 1.6 KHz to 104 KHz. The Bessel filter is an 8th order low pass filter with a linear phase response over its entire passband. It exhibits little to no over-shoot, under-shoot, or ringing with pulse type signals and its cutoff frequency can be programmed from 300Hz to 88 KHz. If desired, the filters can be bypass. In the case, only a fixed 2<sup>nd</sup> order active RC low pass filter with a cutoff frequency of around 400 KHz is provided.

# 3.1.6 Programmable Gain Amplifier (PGA)

The programmable gain amplifier (PGA) provides a programmable (back-end) gain of 1, 2, 5, 10, 20, 50, and 100.

# 3.1.7 Analog Digital Converter (ADC)

The ADC converts the analog input signal to a digital value. The ADC is a 14-bit that uses successive approximation register (SAR) architecture with no pipeline delay to perform the analog-to-digital conversion.

# 3.1.8 Aperture Comparator

The aperture comparator logic provides real-time data compression of the input signal. The aperture comparator logic compares the new data value with the last stored value to provide a real-time decision to store or not store the data. Various aperture modes allow easy storage of only the desired data reducing storage and data transfer requirements. Two programmable apertures (A & B) each with a high and low value allow flexible setting of the desired data. Depending on the aperture mode, the logic can use an external signal switch between the two apertures or automatically switch.

# 3.1.9 FIFO

The synchronous read/write first-in first-out (FIFO<sup>\*</sup>) memory provides data storage for up to 32 million value-time pairs or 64 million A/D values. In value-time pair storage mode, the value-time pairs are stored as 48-bit wide data and retrieved by the user as a three 16-bit word set or as a two 32-bit word set. In value storage only mode, the A/D value is stored in the upper 32-bits of memory and retrieved by the user as a single 16-bit words or as a 32-bit word sets.

\* Note: Although the memory is technically a FIFO, a random access capability is provided to allow the read pointer to be positioned at any point in memory. This capability is very useful in continuous capture mode where the data of interest may be near the end of the FIFO.

# 3.1.10 32-Bit Timestamp

The 32-bit timer provides a time stamp of the data stored. The time increments by one on each rising edge of the sample clock. The timer can be reset independent of the A/D conversion enable or at the same time and can be programmed to continue running while A/D conversion is disabled. Over one hour of uniquely time-stamped data can be captured when running a sample rate of 1M samples per second. A timestamp rollover interrupt allows unique time stamping for an indefinite amount of time.

# 3.1.11 Clock/Run Control

This logic provides selection and control of the sample clock and timestamp run enable signals. These signals can be generated internally or provided by an external source through the front panel or backplane triggers. The logic includes a prescaler that can divide the input clock frequency by a value from 1 to 100,000 to produce the desired sample rate. In addition, the sample clock and timestamp run enable signals can be output to the front panel connector or to the backplane triggers to serve as the master control for multiple M228's in a system.

# 3.1.12 On-board Oscillator

An on-board oscillator provides a base 1MHz to the clock control logic. This oscillator can be used to perform the A/D conversion and time stamping.

# 3.1.13 External Inputs and Control

Two front panel inputs are provided for external control of the sample clock rate, A/D conversion enable, and other signals. Each input has a programmable threshold level, input impedance, and logic inversion capability. In addition, the signals can be internally latched to provide a typical armed, ready, triggered function.

# 3.1.14 External Outputs and Control

Two front panel outputs are provided for external synchronization of other system components. A variety of internal signals can be routed to the front panel outputs.

# 3.1.15 M-Triggers & Control

Two bidirectional backplane triggers (TRIGA/B) allow control the sample clock rate, A/D conversion enable, and other signals through a carrier or system backplane. In addition, a variety of internal signals can be routed and output to the backplane trigger system.

# 3.1.16 Calibration

Calibration is provided through an on-board digital potentiometer that allows adjustment of the 0V offset and full scale reading. Calibration can be performed using on-board references or at a system level using external references. Calibration values are stored in an on-board non-volatile EEPROM.

# 3.2 INPUT/OUTPUT SIGNALS

The front panel I/O connector is a standard 44-pin D-subminiature female receptacle (CONEC P/N 164A18119X or equivalent). Below are the signals and functional descriptions provided on the connector (see Appendix A for pin assignments).

- AIN+/- Differential Analog Input Signals

- FPINA/B Front Panel Input A & B. These contacts can be used to input an external sample clock, A/D conversion enable, or RUN enable signal (Input threshold is programmable from 0V to +5.0V, input impedance is programmable for Hi-Z or 50  $\Omega$ ).

- FPOUTA/B Front Panel Output A & B. These contacts can be programmed to output the master sample clock, A/D conversion enable, or run enable signal (TTL output levels).

- AUX+5V Auxiliary +5V power for an external buffer, amplifier, or other logic. (*Do not* exceed 500mA)

- AUX+12V Auxiliary +12V power for an external buffer, amplifier, or other logic. (*Do not* exceed 100mA)

- AUX-12V Auxiliary -12V power for an external buffer, amplifier, or other logic. (Do not exceed 100mA)

- GND Ground (common ground for the FPINA/B, FPOUTA/B, AUX+5V, AUX+12V, and AUX-12V).

# 3.3 CONFIGURATION AND IDENTIFICATION

# 3.3.1 Programming Registers

There are a variety of registers used to configure and control the M228 module. These registers are located as an offset from the base address of the module. The absolute address depends on the M-module carrier for which the M228 is installed. See the carrier's User Manual for details. The address map and details of the registers are shown in Table I and Figure 9.

| IO REG. |        |                                  |

|---------|--------|----------------------------------|

| (HEX)   | 32-Bit | REGISTER DESCRIPTION             |

| 00      | *      | ID                               |

| 02      |        | Revision                         |

| 04      | *      | Master Control                   |

| 06      |        | Interrupt Control                |

| 08      | *      | Function Source Control          |

| 0A      |        | Clock Control                    |

| 0C      | *      | Output Source Map                |

| OE      |        | (reserved)                       |

| 10      | *      | Input A Control                  |

| 12      |        | Input B Control                  |

| 14      | *      | Aperture High A                  |

| 16      |        | Aperture Low A                   |

| 18      | *      | Aperture High B                  |

| 1A      |        | Aperture Low B                   |

| 1C-1E   |        | (reserved)                       |

| 20      | *      | FIFO Data Port (32-bit/16-bit)   |

| 22      |        | (reserved)                       |

| 24      | *      | FIFO Unread Count (High)         |

| 26      |        | FIFO Unread Count (Low)          |

| 28      | *      | Last Value Stored                |

| 2A      |        | Current Value                    |

| 2C      | *      | Time Stamp (High)                |

| 2E      |        | Time Stamp (Low)                 |

| 30      | *      | Peripheral Variable Voltage      |

| 32      |        | (reserved)                       |

| 34      | *      | Random Data Port (32-bit/16-bit) |

| 36      |        | (reserved)                       |

| 38      | *      | Random Data Address (High)       |

| 3A      |        | Random Data Address (Low)        |

| 3A-3E   |        | (reserved)                       |

| 40      | *      | Analog Input Control             |

| 42      |        | Anti-Aliasing Filter Control     |

| 44      | *      | A/D Temperature                  |

| 46      |        | Calibration Fullscale/Offset     |

| 48      | *      | Calibration EEPROM Control       |

| 4A      |        | Calibration EEPROM Data          |

| 4C-FC   |        | (reserved)                       |

| FE      |        | IDPROM                           |

| Table I.  | Register | Address Map  |

|-----------|----------|--------------|

| I abit Ii | Register | nuul coo mup |

Note: The \* indicates allowable 32-bit access boundaries.

| Reg 00                                                                                                                                                                                                                    | ID Register             |    |    |     |      |    |      |       |      |       |   |    |     |   |   |   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|----|----|-----|------|----|------|-------|------|-------|---|----|-----|---|---|---|

| Bit                                                                                                                                                                                                                       | 15                      | 14 | 13 | 12  | 11   | 10 | 9    | 8     | 7    | 6     | 5 | 4  | 3   | 2 | 1 | 0 |

| Write                                                                                                                                                                                                                     | (read only) (read only) |    |    |     |      |    |      |       |      |       |   |    |     |   |   |   |

| Read                                                                                                                                                                                                                      |                         |    |    | CON | IFIG |    |      |       |      |       |   | MO | DEL |   |   |   |

| <ul> <li>CONFIG ⇒ Configuration Number (dash number of the unit according to the following table)</li> <li>0 Normal</li> <li>Others Undefined</li> <li>MODEL ⇒ Model Number (always reads hex E4, decimal 228)</li> </ul> |                         |    |    |     |      |    |      |       |      |       |   |    |     |   |   |   |

| Reg 02                                                                                                                                                                                                                    |                         |    |    |     |      |    | Revi | ision | Regi | ister |   |    |     |   |   |   |

| Bit                                                                                                                                                                                                                       | 15                      | 14 | 13 | 12  | 11   | 10 | 9    | 8     | 7    | 6     | 5 | 4  | 3   | 2 | 1 | 0 |

LGMAJ  $\Rightarrow$  Logic Major Revision (first major release is 1, prerelease is 0)

(read only)

RESERVED

LGMIN  $\Rightarrow$  Logic Minor Revision (minor releases involve insignificant changes or corrections)

(read only)

LGMIN

LGMAJ

RESERVED ⇒ Reserved (this value should be ignored, it is reserved for special information)

Figure 9. Programming Registers

Write

Read

#### Reg 04

### Master Control Register

| Bit   | 15 | 14 | 13 | 12 | 11   | 10  | 9   | 8   | 7  | 6 | 5 | 4 | 3   | 2    | 1   | 0    |  |

|-------|----|----|----|----|------|-----|-----|-----|----|---|---|---|-----|------|-----|------|--|

| Write | -  | -  | -  | -  | CTSR | CCM | RFF | RTS | ST | Μ | - | - | FST | ASEL | ACE | TRUN |  |

| Read  | FF | HF | OF | NE | TSR  | CCM | 0   | 0   | ST | Μ | 0 | 0 | FST | ASEL | ACE | TRUN |  |

| FF ⇒ | FIFO Full ( | $(1 = \text{full})^{-1}$ |

|------|-------------|--------------------------|

|------|-------------|--------------------------|

- HF  $\Rightarrow$  FIFO Half Full (1 = FIFO is at least half full)

- QF  $\Rightarrow$  FIFO Quarter Full (1 = FIFO is at least one quarter full)

- NE  $\Rightarrow$  FIFO Not Empty (1 = FIFO has at least one time-value pair stored)

- TSR  $\Rightarrow$  Time Stamp Rollover (1 = Time Stamp Rollover occurred)

- CTSR  $\Rightarrow$  Clear Time Stamp Rollover (1 = Clear Time Stamp Rollover status)

- CCM  $\Rightarrow$  Continuous Capture Mode<sup>2</sup> (0 = stop capturing data when FIFO is full (CTF Mode), 1 = continuously capture data even when FIFO is full (CCM))

- RFF  $\Rightarrow$  Reset FIFO (1 = reset)

- RTS  $\Rightarrow$  Reset Time Stamp Counter (1 = reset)

- STM ⇒ Storage Mode

- 00 normal value-time pair storage

- 01 value storage only

- 10 (reserved)

- 11 no storage

- FST  $\Rightarrow$  Force Store (0 = normal operation, 1 = force the storage of any value ignoring aperture values)<sup>3</sup>

- ASEL  $\Rightarrow$  Aperture Select (0 = use "A" aperture values, 1 = use "B" aperture values)<sup>3</sup>

- ACE  $\Rightarrow$  A/D Conversion Enable (0 = disable, 1 = enable)<sup>3,4</sup>

- TRUN  $\Rightarrow$  Timestamp Run (0 = timestamp clock disabled, 1 = timestamp clock enabled)<sup>3</sup>

#### Notes:

- 1. In CTF mode, FIFO Full is an error condition and capturing of data stops. In CCM, FIFO Full is only an indicator.

- 2. See 4.2 for details on operation in these modes.

- 3. The FST, ASEL, ACE and TRUN bits only set the software value for the control. The source of the function must be defined as "Software Register" in the Function Source Control and Clock Control Registers to use these bits.

- 4. When STM = 00, value-time storage can only occur when ACE is enabled. If ACE is disabled and TRUN is enabled, the timestamp counter will run, but no data will be stored.

Figure 9. Programming Registers (continued)

Reg 06

### **Interrupt Control Register**

| Bit   | 15   | 14   | 13   | 12   | 11   | 10 | 9 | 8 | 7    | 6    | 5    | 4    | 3    | 2 | 1 | 0   |

|-------|------|------|------|------|------|----|---|---|------|------|------|------|------|---|---|-----|

| Write | FFIP | HFIP | QFIP | NEIP | TSRP | -  | - | - | FFIE | HFIE | QFIE | NEIE | TSRE | - | - | GIE |

| Read  | FFIP | HFIP | QFIP | NEIP | TSRP | 0  | 0 | 0 | FFIE | HFIE | QFIE | NEIE | TSRE | 0 | 0 | GIE |

FFIP  $\Rightarrow$  FIFO Full Interrupt Pending  $(1 = \text{pending})^1$

HFIP  $\Rightarrow$  FIFO Half Full Interrupt Pending (1 = pending)<sup>1</sup>

QFIP  $\Rightarrow$  FIFO One-Quarter Full Interrupt Pending (1 = pending)<sup>1</sup>

NEIP  $\Rightarrow$  FIFO Not Empty Interrupt Pending (1= pending)<sup>1</sup>

TSRP  $\Rightarrow$  Time Stamp Rollover Interrupt Pending (1 = pending)<sup>1</sup>

FFIE  $\Rightarrow$  FIFO Full Interrupt Enable (1 = enable)

HFIE  $\Rightarrow$  FIFO Half Full Interrupt Enable (1 = enable)

QFIE  $\Rightarrow$  FIFO One-Quarter Full Interrupt Enable (1 = enable)

NEIE  $\Rightarrow$  FIFO Not Empty Interrupt Enable (1 = enable)

TSRE  $\Rightarrow$  Time Stamp Rollover Interrupt Enable (1 = enable)

GIE  $\Rightarrow$  Global Interrupt Enable (1 = enable)<sup>2</sup>

Notes:

1. To clear a pending interrupt, writing a '1' to the interrupt pending bit.

- 2. GIE bit is automatically cleared when an interrupt acknowledge is received. Software must reenable GIE after servicing the interrupt to receive further interrupts.

- 3. During an interrupt acknowledge (IACK) cycle, the upper byte of this register is presented as the interrupt vector.

# **Function Source Control Register**

|           |       |       |         |                                              |          |        |          |         |          |       | •              | 5                   |         |        |       |   |  |

|-----------|-------|-------|---------|----------------------------------------------|----------|--------|----------|---------|----------|-------|----------------|---------------------|---------|--------|-------|---|--|

| Bit       | 15    | 14    | 13      | 12                                           | 11       | 10     | 9        | 8       | 7        | 6     | 5              | 5 4                 | 3       | 2      | 1     | 0 |  |

| Write     | FSL   | F     | FSTSRC  |                                              | ASL      | A      | SELSR    | С       | ACL      |       | ACE            | SRC                 | TRL     | TF     | RUNSR | С |  |

| Read      | FSL   | F     | FSTSRC  |                                              | ASL      | A      | SELSR    | С       | ACL      |       | ACE            | SRC                 | TRL     | Tŀ     | RUNSR | С |  |

| -         |       |       |         |                                              |          |        |          |         |          |       |                |                     |         |        |       |   |  |

|           | ]     | FSL ⊏ | > Force | e Sto                                        | re All A | Active | Level (  | (0 = a) | ctive hi | gh, 1 | = ac           | tive low)           |         |        |       |   |  |

|           | FSTS  | RC =  | > Forc  | e Sto                                        | re All S | Source | e        |         |          |       |                |                     |         |        |       |   |  |

|           |       |       | 000     | ) Se                                         | oftware  | e Regi | ster (FA | ACQ     | bit)     | 1     | 00             | Backpla             | ne Trig | gger A |       |   |  |

|           |       |       | 001     | l (r                                         | eserve   | 1)     |          |         |          | 1     | 01             | Backpla             | ne Trig | gger B |       |   |  |

|           |       |       | 010     | ) F                                          | PINA s   | signal |          |         |          | 1     | 10             | (reserve            | d)      |        |       |   |  |

|           |       |       | 011     | l F                                          | PINB s   | signal |          |         |          | 1     | 111 (reserved) |                     |         |        |       |   |  |

|           | I     | ASL ⊏ | Aper    | ture S                                       | Select A | Active | Level (  | 0 = ac  | ctive hi | gh, 1 | = ac           | tive low)           |         |        |       |   |  |

| A         | ASELS | RC =  | > Aper  | ture S                                       | Select S | Source | e        |         |          |       |                |                     |         |        |       |   |  |

|           |       |       | 000     | ) Se                                         |          |        |          |         |          |       |                | Backplane Trigger A |         |        |       |   |  |

|           |       |       | 001     | l (r                                         | eserve   | 1)     |          |         |          | 1     | 01             | Backpla             | ne Trig | gger B |       |   |  |

|           |       |       | 010     | ) F                                          | PINA s   | signal |          |         |          | 1     | 10             | (reserve            | d)      |        |       |   |  |

|           |       |       | 011     |                                              | PINB s   |        |          |         |          |       | 11             | (reserve            |         |        |       |   |  |

|           | A     | ACL □ | ⇒ A/D   | A/D Conversion Enable Active Level $(0 = a)$ |          |        |          |         |          |       | e hig          | h, $1 = act$        | ive lov | v)     |       |   |  |

|           | ACES  | RC =  | ⇒ A/D   | Conv                                         | resion   | Enabl  | e Sourc  | ce      |          |       |                |                     |         |        |       |   |  |

|           |       |       | 000     | ) Se                                         | oftware  | e Regi | ster (A  | CE bi   | t)       |       | 00             |                     |         |        |       |   |  |

|           |       |       | 001     | l (r                                         | eserve   | d)     |          |         |          | 1     | 01             | Backpla             | ne Trig | gger B |       |   |  |

|           |       |       | 010     |                                              | PINA s   |        |          |         |          | 1     | 10             | (reserve            | /       |        |       |   |  |

|           |       |       | 011     |                                              | PINB s   |        |          |         |          |       | 11             | (reserve            |         |        |       |   |  |

|           |       |       |         | Timestamp Run Enable Active Level $(0 = a)$  |          |        |          |         |          |       | higl           | 1, 1 = action       | ive low | ')     |       |   |  |

| Т         | RUNS  | RC □  | > Time  | estamp Run Enable Source                     |          |        |          |         |          |       |                |                     |         |        |       |   |  |

|           |       |       | 000     |                                              | oftware  | e Regi | ster (R  | UN bi   | t)       |       | 00             | Backpla             |         |        |       |   |  |

|           |       |       | 001     |                                              | eserve   | ·      |          |         |          | 1     | 01             | Backpla             |         | gger B |       |   |  |

|           |       |       | 010     |                                              | 8        |        |          |         |          |       | 10             | (reserve            | ·       |        |       |   |  |

| 011 FPINB |       |       |         |                                              |          |        | ignal    |         |          |       | 11             | 1 (reserved)        |         |        |       |   |  |

|           |       |       |         |                                              |          |        |          |         |          |       |                |                     |         |        |       |   |  |

### **Clock/Aperture Control Register**

| Bit   | 15   | 14 | 13 | 12 | 11 | 10 | 9    | 8  | 7 | 6  | 5  | 4 | 3 | 2 | 1      | 0 |

|-------|------|----|----|----|----|----|------|----|---|----|----|---|---|---|--------|---|

| Write | SCLK | -  | -  | -  | -  | Α  | PMOE | ЭE |   | PS | SC |   | - | ( | CLKSRO |   |

| Read  | 0    | 0  | 0  | 0  | 0  | А  | PMOE | ЭE |   | PS | SC |   | 0 | ( | 5      |   |

SCLK  $\Rightarrow$  Software Clock (1 = toggles sample clock high then low)<sup>1, 2</sup>

APMODE ⇒ Aperture Mode

- 0 Store if outside selected aperture window

- Store once outside selected "absolute" window and outside of aperture window "B"3 1

- 2 Store if outside absolute window "A" and outside of aperture window "B"

- Store once inside selected absolute window and outside of aperture window "B"3 3

- 4 Store if inside absolute window "A" and outside of aperture window "B"

- 5 Store if outside both absolute window "A" and "B"

- Store if inside either absolute window "A" or "B" 6

- (reserved) 7

PSC ⇒ Prescaler Control (Selected clock is divided by this prescaler)

|          | Value    | Prescaler     | Value      | Prescaler | Value | Prescaler  | Value     | Prescaler |

|----------|----------|---------------|------------|-----------|-------|------------|-----------|-----------|

|          | 0000     | 1             | 0100       | 20        | 1000  | 500        | 1100      | 10000     |

|          | 0001     | 2             | 0101       | 50        | 1001  | 1000       | 1101      | 20000     |

|          | 0010     | 5             | 0110       | 100       | 1010  | 2000       | 1110      | 50000     |

|          | 0011     | 10            | 0111       | 200       | 1011  | 5000       | 1111      | 100000    |

| CLKSRC ⇒ | Clock So | ource         |            |           |       |            |           |           |

|          | 000      | Internal Osci | llator     |           | 100   | Backplane  | Trigger A |           |

|          | 001      | Software Re   | gister (SC | LK bit)   | 101   | Backplane  | Trigger B |           |

|          | 010      | FPINA signa   | ıl         |           | 110   | (reserved) |           |           |

|          | 011      | FPINB signa   | ıl         |           | 111   | (reserved) |           |           |

|          |          |               |            |           |       |            |           |           |

Notes:

- 1. The Clock Source (CLKSRC) field must first be specified as "Software Register" before writing a '1' to the SCLK bit.

- Writing a '1' to SCLK field, produces an internal high then low pulse. 2.

- Once the signal crosses outside (or inside) the absolute window "A" the aperture window "B" is used. 3. A Reset FIFO (RFF) is required to use aperture "A" again.

Reg 0C

### **Output Source Map Register**

| Bit   | 15   | 14 | 13    | 12 | 11   | 10 | 9     | 8 | 7    | 6 | 5     | 4 | 3    | 2 | 1     | 0 |

|-------|------|----|-------|----|------|----|-------|---|------|---|-------|---|------|---|-------|---|

| Write | ITOB |    | TBSRC |    | ITOA |    | TASRC |   | IFOB |   | FBSRC |   | IOFA |   | FASRC |   |

| Read  | ITOB |    | TBSRC |    | ITOA |    | TASRC |   | IFOB |   | FBSRC |   | IOFA |   | FASRC |   |

ITOA/ITOB ⇒ Invert Trigger Output

TASRC/TBSRC

| TASKC/TBSKC - | → I rigge | er Output Source               |

|---------------|-----------|--------------------------------|

|               | 0         | Disabled (input)               |

|               | 1         | Sample Clock (after prescaler) |

|               | 2         | Clock (before prescaler)       |

|               | 3         | Force Store Signal             |

| IFOA/IFOB □   | ⇒ Invert  | Front Panel Output             |

| FASRC/FBSRC = | ⇒ Front   | Panel Output Source            |

|               | 0         | Disabled (High-Z)              |

|               | 1         | Sample Clock (after prescaler) |

- Clock (before prescaler) 2

- 3 Force Store Signal

- 4 Aperture Select Signal

- A/D Conversion Enable Signal 5

- Timestamp Run Enable Signal 6

- 7 Value Stored Strobe

Aperture Select Signal 4

- 5 A/D Conversion Enable Signal

- Timestamp Run Enable Signal 6

- Value Stored Strobe 7

Figure 9. Programming Registers (continued)

# **Input A Control Register**

| Bit   | 15   | 14   | 13 | 12   | 11   | 10   | 9   | 8   | 7 | 6 | 5       | 4       | 3      | 2      | 1 | 0 |

|-------|------|------|----|------|------|------|-----|-----|---|---|---------|---------|--------|--------|---|---|

| Write | CLTA | CLFA | -  | IIFA | IVTA | IVFA | LTA | LFA |   |   | Input T | hreshol | d FP A | (ITFA) |   |   |

| Read  | TAS  | FAS  | 0  | IIFA | IVTA | IVFA | LTA | LFA |   |   | Input T | hreshol | d FP A | (ITFA) |   |   |

| CLTA ⇒ | Clear Latched TRIGINA (1 = clears latched signal) $^{1}$                |

|--------|-------------------------------------------------------------------------|

| CLFA ⇒ | Clear Latched FPINA (1 = clears latched signal) $^{1}$                  |

| TAS ⇒  | TRIGINA Status ( $0 = low$ , $1 = high$ , after inversion and latching) |

| FAS ⇒  | FPINA Status ( $0 = low$ , $1 = high$ , after inversion and latching)   |

| IIFA ⇒ | FPINA Input Impedance ( $0 = \text{Hi-Z}, 1 = 50\Omega$ )               |

| IVTA ⇒ | Invert TRIGINA Input $(0 = normal, 1 = invert)$                         |

| IVFA ⇒ | Invert FPINA ( $0 = normal, 1 = invert$ )                               |

| LTA ⇒  | Latch TRIGINA Input (0 = no latching, 1 = latch on rising edge) $^{2}$  |

| LFA ⇒  | Latch FPINA (0 = no latching, 1 = latch on rising edge) <sup>2</sup>    |

ITFA  $\Rightarrow$  Input Threshold Level of FPINA ( $00_{16} = 0V$  (default), FF<sub>16</sub> = +5V)

Notes:

1. The latched value is cleared by writing a '1' to the CLTA or CLFA bit.

2. Latching occurs on the rising edge of the signal after inversion, if specified.

#### Reg 12

# **Input B Control Register**

| Bit   | 15   | 14   | 13 | 12   | 11   | 10   | 9   | 8   | 7                           | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|------|------|----|------|------|------|-----|-----|-----------------------------|---|---|---|---|---|---|---|--|

| Write | CLTB | CLFB | -  | IIFB | IVTB | IVFB | LTB | LFB | Input Threshold FP B (ITFB) |   |   |   |   |   |   |   |  |

| Read  | TBS  | FBS  | 0  | IIFB | IVTB | IVFB | LTB | LFB | Input Threshold FP B (ITFB) |   |   |   |   |   |   |   |  |

| ;)   |

|------|

|      |

|      |

|      |

|      |

| 2    |

|      |

| +5V) |

| ))   |

Notes:

1. The latched value is cleared by writing a '1' to the CLTB or CLFB bit.

2. Latching occurs on the rising edge of the signal after inversion, if specified.

| Reg 14 |    |    |    |    |    | Ape | rtur | e Hig | gh A     | Regi    | ster |   |   |   |   |   |

|--------|----|----|----|----|----|-----|------|-------|----------|---------|------|---|---|---|---|---|

| Bit    | 15 | 14 | 13 | 12 | 11 | 10  | 9    | 8     | 7        | 6       | 5    | 4 | 3 | 2 | 1 | 0 |

| Write  | -  | -  |    |    |    |     |      | Ape   | erture H | igh A V | alue |   |   |   |   |   |

| Read   | 0  | 0  |    |    |    |     |      | Ape   | erture H | igh A V | alue |   |   |   |   |   |

Aperture High A  $\Rightarrow$  This value is used to determine if the A/D value is stored to memory. The storage criterion depends on the Aperture Mode.

Note: See note below.

| Reg 16 |    |    |    |    |    | Ape | ertur | e Lo | w A ]     | Regi   | ster |   |   |   |   |   |

|--------|----|----|----|----|----|-----|-------|------|-----------|--------|------|---|---|---|---|---|

| Bit    | 15 | 14 | 13 | 12 | 11 | 10  | 9     | 8    | 7         | 6      | 5    | 4 | 3 | 2 | 1 | 0 |

| Write  | -  | -  |    |    |    |     |       | Apo  | erture Lo | ow A V | alue |   |   |   |   |   |

| Read   | 0  | 0  |    |    |    |     |       | Ар   | erture L  | ow A V | alue |   |   |   |   |   |

Aperture Low A ⇒ This value is used to determine if the A/D value is stored to memory. The storage criterion depends on the Aperture Mode.

Note: See note below.

| Reg 18 |    |    |    |    |    | Ape | rtur | e Hiş | gh B     | Regi    | ster |   |   |   |   |   |

|--------|----|----|----|----|----|-----|------|-------|----------|---------|------|---|---|---|---|---|

| Bit    | 15 | 14 | 13 | 12 | 11 | 10  | 9    | 8     | 7        | 6       | 5    | 4 | 3 | 2 | 1 | 0 |

| Write  | -  | -  |    |    |    |     |      | Apo   | erture H | igh B V | alue |   |   |   |   |   |

| Read   | 0  | 0  |    |    |    |     |      | Ap    | erture H | igh B V | alue |   |   |   |   |   |

Aperture High B ⇒ This value is used to determine if the A/D value is stored to memory. The storage criterion depends on the Aperture Mode

Note: See note below.

Reg 1A

# Aperture Low B Register

| Bit   | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8   | 7        | 6      | 5    | 4 | 3 | 2 | 1 | 0 |

|-------|----|----|----|----|----|----|---|-----|----------|--------|------|---|---|---|---|---|

| Write | -  | -  |    |    |    |    |   | Apo | erture L | ow B V | alue |   |   |   |   |   |

| Read  | 0  | 0  |    |    |    |    |   | Ар  | erture L | ow B V | alue |   |   |   |   |   |

Aperture Low B  $\Rightarrow$  This value is used to determine if the A/D value is stored to memory. The storage criterion depends on the Aperture Mode.

Note: Aperture values are always specified as two's complement numbers, which represent both positive and negative values. When specifying an aperture window (versus a fixed window), the user must ensure that only positive values are specified.

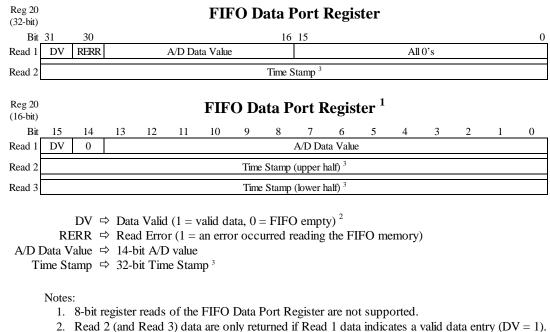

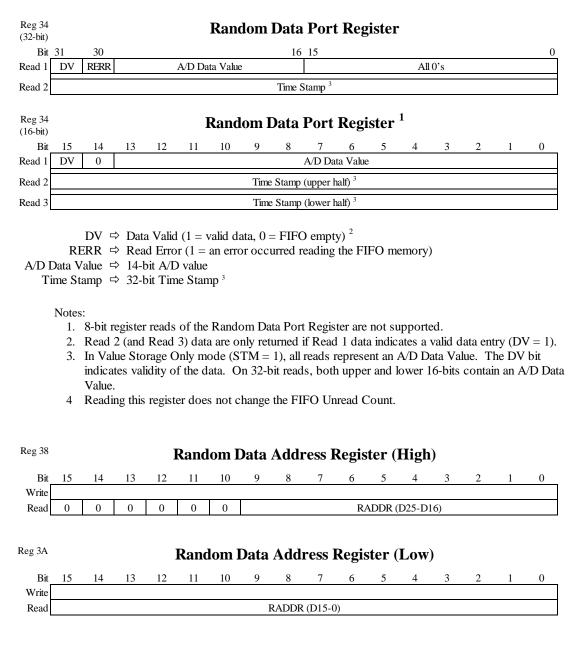

Read 2 (and Read 3) data are only returned if Read 1 data indicates a valid data entry (DV = 1).

In Value Storage Only mode (STM = 1), all reads represent an A/D Data Value. The DV bit indicates validity of the data. On 32-bit reads, both upper and lower 16-bits contain an A/D Data Value.

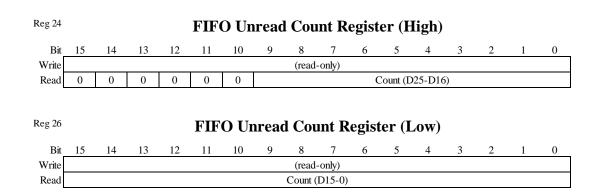

Count  $\Rightarrow$  Number of time-value pairs that have not been read by the user.

Notes:

- 1. To guarantee consistency between the High and Low registers when reading as 16-bit words, the High register must be read first. Internally, the Low register is latched when the High register is read.

- 2. In Value Storage Only mode (STM = 1), the FIFO is treated as 16 bits wide; therefore, the unread count represents one data entry.

| Reg 28 |         |        |       |       |         | Last    | : Val  | ue St   | ored     | Reg     | ister |        |        |        |        |        |

|--------|---------|--------|-------|-------|---------|---------|--------|---------|----------|---------|-------|--------|--------|--------|--------|--------|

| Bit    | 15      | 14     | 13    | 12    | 11      | 10      | 9      | 8       | 7        | 6       | 5     | 4      | 3      | 2      | 1      | 0      |

| Write  |         |        |       |       |         |         |        | (read   | -only)   |         |       |        |        |        |        |        |

| Read   | 0       | 0      |       |       |         |         |        |         | Last S   | stored  |       |        |        |        |        |        |

| L      | ast Sto | ored 🛛 | ⇒ Las | t A/D | value s | tored i | n FIF( | С       |          |         |       |        |        |        |        |        |

| Reg 2A |         |        |       |       |         | Cu      | irren  | nt Va   | lue R    | legist  | ter   |        |        |        |        |        |

| Bit    | 15      | 14     | 13    | 12    | 11      | 10      | 9      | 8       | 7        | 6       | 5     | 4      | 3      | 2      | 1      | 0      |

| Write  |         |        |       |       |         |         |        | (read   | -only)   |         |       |        |        |        |        |        |

| Read   | 0       | 0      |       |       |         |         |        |         | Curren   | t Value |       |        |        |        |        |        |

|        | This    | regist |       | dated | after e |         |        |         | on; the  | refore, | A/D c | conver | sion m | ust be | enable | ed and |

| Reg 2C |         |        |       |       |         | Time    | e Sta  | mp R    | Regist   | er (H   | ligh) | 1      |        |        |        |        |

| Bit    | 15      | 14     | 13    | 12    | 11      | 10      | 9      | 8       | 7        | 6       | 5     | 4      | 3      | 2      | 1      | 0      |

| Write  |         |        |       |       |         |         |        | (read   | -only)   |         |       |        |        |        |        |        |

| Read   |         |        |       |       |         |         | Tim    | e Stamp | ) (D31-I | D16)    |       |        |        |        |        |        |

| Reg 2E |         |        |       |       |         | Time    | e Sta  | mp F    | Regist   | ter (l  | Low)  |        |        |        |        |        |

| Bit    | 15      | 14     | 13    | 12    | 11      | 10      | 9      | 8       | 7        | 6       | 5     | 4      | 3      | 2      | 1      | 0      |

| Write  |         |        |       |       |         |         |        | (road   | onki)    |         |       |        |        |        |        |        |

| Write | (read-only)        |

|-------|--------------------|

| Read  | Time Stamp (D15-0) |

|       |                    |

Time Stamp  $\Rightarrow$  Snapshot of current Time Stamp value.

Note: To guarantee consistency between the High and Low registers when reading as 16-bit words, the High register must be read first. Internally, the Low register is latched when the High register is read.

| Reg 30 |    |    |    |    | Perij | phera | al Va | riab | le Vo | oltage | e Reg | gister | • |   |   |   |

|--------|----|----|----|----|-------|-------|-------|------|-------|--------|-------|--------|---|---|---|---|

| Bit    | 15 | 14 | 13 | 12 | 11    | 10    | 9     | 8    | 7     | 6      | 5     | 4      | 3 | 2 | 1 | 0 |

| Write  | -  | -  | -  | -  |       |       |       |      |       | PVA    | ARV   |        |   |   |   |   |

| Read   | 0  | 0  | 0  | 0  |       |       |       |      |       | PVA    | ARV   |        |   |   |   |   |

$PVARV \Rightarrow$  Peripheral Variable Voltage Level ( $000_{16} = -10V$  (default),  $800_{16} = 0V$ ,  $FFF_{16} = +10V$ )

RADDR ⇒ FIFO Memory Address to access when the Random Data Port Register is read

Notes:

- 1. To guarantee consistency between the High and Low registers when reading as 16-bit words, the High register must be read first. Internally, the Low register is latched when the High register is read.

- 2. In Value Storage Only mode (STM = 1), the FIFO is treated as 16 bits wide; therefore, the unread count represents one data entry.

- 3. This register automatically increments each time the Random Data Port Register is read.

Reg 40

### **Analog Input Control Register**

| Bit   | 15   | 14 | 13     | 12 | 11 | 10 | 9  | 8    | 7    | 6 | 5   | 4   | 3 | 2 | 1     | 0 |

|-------|------|----|--------|----|----|----|----|------|------|---|-----|-----|---|---|-------|---|

| Write | REFE |    | REFSEL |    | SI | М  | FT | WARP | IVDD | - | FGA | AIN | - |   | BGAIN |   |

| Read  | REFE |    | REFSEL |    | SI | М  | FT | WARP | IVDD | 0 | FGA | AIN | 0 |   | BGAIN |   |

### REFE $\Rightarrow$ Reference Enable (0 = normal operation, 1 = enable reference signal injection)

| REFSEL | ⇒ | Refer | ence Select               |      |                                                                                   |

|--------|---|-------|---------------------------|------|-----------------------------------------------------------------------------------|

|        |   | 0     | Ground (0V)               |      |                                                                                   |

|        |   | 1     | 0.5V                      |      |                                                                                   |

|        |   | 2     | -0.5V                     |      |                                                                                   |

|        |   | 3     | 10V                       |      |                                                                                   |

|        |   | 4     | -10V                      |      |                                                                                   |

|        |   | 5     | Variable <sup>1</sup>     |      |                                                                                   |

|        |   | 6     | +5V Supply                |      |                                                                                   |

|        |   | 7     | +3.3V Supply <sup>1</sup> |      |                                                                                   |

| SIM    | ⇒ | Simul | ation Mode (non           | -zer | ro = simulate a full scale triangle waveform input)2                              |

|        |   | 0     | Normal Mode               |      |                                                                                   |

|        |   | 1     | Count Up from mid         | poin | tt                                                                                |

|        |   | 2     | Count Down from           | nidp | oint                                                                              |

|        |   | 3     | (reserved)                |      | 2                                                                                 |

|        |   |       | •                         |      | operation, $1 = \text{factory test mode})^3$                                      |

|        |   |       |                           |      | node ( $\leq$ 800KSPS), 1 = fast conversion rate mode ( $>$ 800KSPS) <sup>4</sup> |

| IVDD   | ⇒ | Input | Voltage Divider           | Disa | able (0 = enabled - $10:1(default), 1 = disabled - 1:1)$                          |

| FGAIN  | ⇒ | Front | End Gain                  |      |                                                                                   |

|        |   | 0     | G = 1                     |      |                                                                                   |

|        |   | 1     | G = 2                     |      |                                                                                   |

|        |   | _     | G = 5                     |      |                                                                                   |

|        |   | 3     | G = 10                    |      |                                                                                   |

| BGAIN  | ⇒ |       | End Gain                  |      |                                                                                   |

|        |   |       | G = 1                     |      | G = 20                                                                            |

|        |   | 1     | G = 2                     |      | G = 50                                                                            |

|        |   |       | G = 5                     |      |                                                                                   |

|        |   | 3     | G = 10                    | 7    | G = 0 (disables output)                                                           |

Notes:

- The variable voltage (PVARV), +5V Supply, and +3.3V Supply can be used to perform general self test functions. They should NOT be used to perform calibration. The PVARV level is controlled using the Peripheral Variable Voltage Register (Reg 26).

- 2. The simulation mode can be used to verify internal operation of the memory, control and aperture logic. In this mode, full scale triangle wave data is simulated and returned at the sample clock rate.

- 3. In Factory Test mode, the upper 16-bits of the Timestamp equal the 1's complement of the lower sixteen bits.

- 4. For sample frequencies >800KSPS, the A/D must be set to Warp Mode. See 4.1 for details about the A/D behavior in this mode.

### **Anti-Aliasing Filter Control Register**

| Bit   | 15   | 14    | 13      | 12    | 11                | 10    | 9      | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1  | 0  |

|-------|------|-------|---------|-------|-------------------|-------|--------|---|---|---|---|---|---|---|----|----|

| Write | -    | -     | -       | -     |                   | FCU   | IOFF   |   | - | - | - | - | - | - | FS | EL |

| Read  | 0    | 0     | 0       | 0     |                   | FCU   | IOFF   |   | 0 | 0 | 0 | 0 | 0 | 0 | FS | EL |

|       |      |       |         |       | •                 |       |        |   |   |   |   |   |   |   |    |    |

| ]     | FCUT | OFF 🛛 | ⇒ Filte | r Cut | off Freq          | uency |        |   |   |   |   |   |   |   |    |    |

|       |      |       |         |       | Elliptic          |       | Bessel |   |   |   |   |   |   |   |    |    |

|       |      |       |         | 0     | 1.6KHz            | 3     | 00Hz   |   |   |   |   |   |   |   |    |    |

|       |      |       |         | 1     | 3.2KHz            | 6     | 00Hz   |   |   |   |   |   |   |   |    |    |

|       |      |       |         | 2     | 6.5KHz            | 1     | .4KHz  |   |   |   |   |   |   |   |    |    |

|       |      |       |         | 3     | 13KHz             | 2     | .8 KHz |   |   |   |   |   |   |   |    |    |

|       |      |       |         | 4     | 26KHz             | 5     | .5 KHz |   |   |   |   |   |   |   |    |    |

|       |      |       |         | 5     | 52KHz             |       | 1 KHz  |   |   |   |   |   |   |   |    |    |

|       |      |       |         | 6     | 104KHz            |       | 2 KHz  |   |   |   |   |   |   |   |    |    |

|       |      |       |         | 7     | Invalid           |       | 4 KHz  |   |   |   |   |   |   |   |    |    |

|       |      |       |         | 8     | Invalid           | 8     | 8 KHz  |   |   |   |   |   |   |   |    |    |

|       |      |       |         | -15   | Invalid           |       | nvalid |   |   |   |   |   |   |   |    |    |

|       | F    | SEL □ | ⇒ Filte | r Typ | e Select          |       |        |   |   |   |   |   |   |   |    |    |

|       |      |       | 0       |       | bass <sup>1</sup> |       |        |   |   |   |   |   |   |   |    |    |

|       |      |       | 1       | Ellip |                   |       |        |   |   |   |   |   |   |   |    |    |

|       |      |       | 2       |       |                   |       |        |   |   |   |   |   |   |   |    |    |

|       |      |       | 3       | inva  | lid               |       |        |   |   |   |   |   |   |   |    |    |

Note: When Bypass is selected, the elliptic and Bessel filters are bypassed; however, a fixed 2<sup>nd</sup> order active RC filter with a cutoff frequency of 400 KHz is still in place to eliminate unwanted high frequency signals.

Reg 44

### **A/D** Temperature Register

| Bit   | 15  | 14 | 13 | 12 | 11 | 10 | 9    | 8 | 7 | 6 | 5  | 4       | 3  | 2 | 1 | 0 |

|-------|-----|----|----|----|----|----|------|---|---|---|----|---------|----|---|---|---|

| Write | DTR | -  | -  | -  | -  | -  | -    |   |   |   | (r | ead-onl | y) |   |   |   |

| Read  | DTR | 0  | 0  | 0  | 0  | 0  | NEGT |   |   |   | A  | DTEM    | Р  |   |   |   |

DTR  $\Rightarrow$  Disable Temperature Read (1 = disable temperature reading)<sup>1</sup>

NEGT  $\Rightarrow$  Negative Temperature (1 = the temperature is below zero)

ADTEMP ⇒ A/D Temperature Value

NEGT Temperature Formula

0 ADTEMP ÷ 4 1 (ADTEMP - 512) ÷ 4

Note: Reading of the A/D board temperature is performed every 0.5 seconds through a serial bus protocol. The DTR bit is provided to allow this automatic operation to be disabled for cases where noise reduction is crucial.

| Bit   | 15 | 14 | 13 | 12  | 11  | 10 | 9 | 8 | 7 | 6 | 5 | 4   | 3   | 2 | 1 | 0 |

|-------|----|----|----|-----|-----|----|---|---|---|---|---|-----|-----|---|---|---|

| Write |    |    |    | FS  | /AL |    |   |   |   |   |   | OSV | VAL |   |   |   |

| Read  |    |    |    | FSV | /AL |    |   |   |   |   |   | OSV | VAL |   |   |   |

FSVAL  $\Rightarrow$  Full-scale Calibration Value (default = 0x80)

OSVAL  $\Rightarrow$  Offset Calibration Value (default = 0x80)

#### Notes:

- 1. This register controls digital potentiometers that do not retain their settings when powered off. Application driver software must initialize the calibration potentiometers before using the A/D converter.

- 2. Data is automatically read-back from the calibration potentiometers after reset/initialization and after a write to this register.

- 3. The OPC flag in the Calibration EEPROM Control Register goes low when the write operation is started and high when the data write and read-back operations are complete.

### **Calibration EEPROM Control Register**

| Bit   | 15  | 14   | 13  | 12  | 11 | 10 | 9 | 8 | 7 | 6 | 5  | 4  | 3 | 2 | 1 | 0 |

|-------|-----|------|-----|-----|----|----|---|---|---|---|----|----|---|---|---|---|

| Write | -   | -    | WPR | RPR | -  | -  | - |   |   |   | AD | DR |   |   |   | - |

| Read  | OPC | IERR | 0   | 0   | 0  | 0  | 0 |   |   |   | AD | DR |   |   |   | 0 |

OPC  $\Rightarrow$  Operation Complete (0 = working, 1 = done)<sup>1</sup>

IERR  $\Rightarrow$  Internal Bus (I2C) Error (1 = an error occurred)<sup>2</sup>

WPR  $\Rightarrow$  Write EEPROM Value (1 = write)<sup>3</sup>

RPR  $\Rightarrow$  Read EEPROM Value (1 = read)<sup>4</sup>

WADDR ⇒ Set EEPROM Write Address (address is word aligned)

#### Notes:

Reg. 48

- 1. The OPC flag goes low when an operation is started and high when the operation is complete. Software must always check the OPC flag before attempting an operation. See special note for EEPROM write operations.

- 2. This bit indicates an error occurred on the last internal I2C bus operation, which is used for the EEPROM, Full Scale & Offset adjust, A/D temperature reading, and reference select operations.

- 3. When a 1 is written to the WPR bit, the EEDATA in the Calibration EEPROM Data Register is written to the EEPROM address specified in the ADDR field. Allow an additional 5ms after the OPC flag before performing another EEPROM operation.

- 4. When a 1 is written to RPR bit, the data at location ADDR is read and placed in the Calibration EEPROM Data Register. The OPC will go high when the read is complete and the EEDATA value is valid.

# **Calibration EEPROM Data Register**

| Bit   | 15     | 14 | 13 | 12 | 11 | 10 | 9 | 8   | 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|--------|----|----|----|----|----|---|-----|-----|---|---|---|---|---|---|---|

| Write | EEDATA |    |    |    |    |    |   |     |     |   |   |   |   |   |   |   |

| Read  |        |    |    |    |    |    |   | EED | ATA |   |   |   |   |   |   |   |

Notes:

Reg. 4A

- 1. A read/write is performed from/to the address in the ADDR field in the Calibration EEPROM Control Register.

- The OPC flag in the Calibration EEPROM Control Register goes low when an operation is started and high when the operation is complete. Software must always check the OPC flag before attempting an operation. Write operations can take up to 5ms to complete. Read operations complete in less than 1ms.

# **IDPROM Register**

| Bit   | 15       | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7  | 6   | 5   | 4 | 3 | 2  | 1   | 0   |

|-------|----------|----|----|----|----|----|---|---|----|-----|-----|---|---|----|-----|-----|

| Write | Not Used |    |    |    |    |    |   |   | CS | CLK | DIO |   |   |    |     |     |

| Read  |          |    |    |    |    |    | 0 |   |    |     |     |   |   | CS | CLK | DIO |

$\begin{array}{rcl} CS & \rightleftharpoons & IDPROM & Chip & Select \\ CLK & \Leftrightarrow & IDPROM & Clock \\ DIO & \Leftrightarrow & IDPROM & Data & Input/Output \end{array}$

### 3.3.2 M-Module Identification PROM

The M228 supports the identification function called IDENT. This IDENT function provides information about the module and is stored in a sixteen-word deep (32 byte) serial EEPROM. Access is accomplished with read/write operations on the last address in IOSpace (0xFE) and the data is read one bit at a time. Instructions for reading the IDENT PROM are given in section 4.6.

The module also supports the VXI-IDENT function. This function is <u>not</u> part of the approved ANSI/VITA 12-1996 standard. This extension to the M-module IDENT function increases the size of the EEPROM to at least 64 words (128 bytes) and includes VXI compatible ID and Device Type Registers. Details are shown in Table II.

| Word  | Description                         | Value (hex)     |

|-------|-------------------------------------|-----------------|

| 0     | Sync Code                           | 5346            |

| 1     | Module Number                       | 00E4 (228 dec.) |

| 2     | Revision Number <sup>1</sup>        | 1010            |

| 3     | Module Characteristics <sup>2</sup> | 1E70            |

| 4-7   | Reserved                            | 0000            |

| 8-15  | M-Module Specific                   | 0000            |

| 16    | VXI Sync Code                       | ACBA            |

| 17    | VXI ID                              | 0FC1 (C&H)      |

| 18    | VXI Device Type <sup>3</sup>        | FFD4            |

| 19-31 | Reserved                            | 0000            |

| 32-63 | M-Module Specific                   | 0000            |

Table II. M-Module EEPROM IDENT Words

Notes:

- The Revision Number is the logic firmware and hardware functional revision level of the module. The hardware revision number does not necessarily correspond to the hardware assembly level. The bits definitions are:

- Bit(s) Description

- 15-12 Software Major Revision (1.0 is first major release)

- 11-8 Software Minor Revision

- 7-4 Hardware Major Revision (1.0 is first major release)

- 3-0 Hardware Minor Revision

- 2) The Module Characteristics bit definitions are: