USER'S MANUAL

# SLEWABLE FUNCTION GENERATOR INDUSTRY PACK

MODEL IP202S

#### **COPYRIGHT**

C&H Technologies, Inc. (C&H) provides this manual "as is" without warranty of any kind, either expressed or implied, including but not limited to the implied warranties of merchantability and fitness for a particular purpose. C&H may make improvements and/or changes in the product(s) and/or program(s) described in this manual at any time and without notice.

This publication could contain technical inaccuracies or typographical errors. Changes are periodically made to the information herein; these changes will be incorporated in new editions of this publication.

#### Copyright © 1998, 2002 by C&H Technologies, Inc.

The information and/or drawings set forth in this document and all rights in and to inventions disclosed herein which might be granted thereon disclosing or employing the materials, methods, techniques or apparatus described herein, are the exclusive property of C&H Technologies, Inc.

A Reader's Comment Form is provided at the back of this publication. If this form has been removed address comments to:

C&H Technologies, Inc. Technical Publications 445 Round Rock West Drive Round Rock, Texas 78681-5012

C&H may use or distribute any of the information you supply in any way that it believes appropriate without incurring any obligations whatever.

#### **MODULE WARRANTY**

C&H Technologies, Inc. warrants its modules to be free from defects in material and workmanship for three years from date of shipment. C&H will repair or replace the defective product without charge within the warranty period, provided the defective item is shipped, freight prepaid, to C&H Technologies, at 15809 Vision Drive, Pflugerville, TX 78660. C&H will pay return freight charges to any point in the continental United States or Canada.

Obligations under this warranty shall be limited to repair or replacement, at C&H's discretion, of any product or part thereof which has been returned by the original purchaser with transportation prepaid and, upon examination by C&H, found to be defective. C&H assumes no responsibility for loss or damage to equipment being returned for repair or replacement under the terms of this warranty. Equipment which, upon examination by C&H, requires repair or replacement of parts thereof as a result of improper installation, misuse, unauthorized alterations or repairs, or user negligence, will have such repairs or replacement of parts made at then current rates.

This warranty does not cover damage caused by misuse, neglect, accident, or improper application or installation. C&H shall not be liable for consequential damages of any kind arising out of the purchase, installation, use or misuse of the product. C&H makes no representation or warranty of any kind, either expressed or implied, with respect to equipment operation or procedures. Any action that the user may take in reliance upon the operation or accuracy of this equipment shall be taken solely at the user's own responsibility and risk.

Please notify the C&H sales department to obtain a Return Authorization Number (RAN) prior to return of a product under the terms of this warranty. Notification is to include the Model and Serial numbers of the product along with full details of the problem. Modules returned should clearly show the RAN on the outside of the package.

#### **AMENDMENT NOTICE**

C&H Technologies, Inc. makes every attempt to provide up-to-date manuals with the associated equipment. Occasionally, changes are made to the equipment wherein it is necessary to provide amendments to the manual. If any amendments are provided for this manual they are printed on colored paper and will be provided with the module and manual.

#### NOTE

The contents of any amendment may affect operation, maintenance, or calibration of the equipment.

#### **INTRODUCTION**

This manual describes the operation and use of the C&H Model IP202S Industry Pack Module (Part Number 11027720 Rev. A of higher). This mezzanine module is designed to interface within any Industry Pack carrier adhering to the ANSI/VITA 4-1995 IndustryPack® standard. These carriers are available in many formats such as VME, VXI, PXI, PC-AT, PCI, and cPCI. C&H provides two carriers (Models VX403B and VX403C) that allows up to four standard Industry Pack modules to be installed in a single VXI slot.

Contained within this manual are the physical and electrical specifications, installation and startup procedures, functional description, and configuration and programming guidelines to adequately use the product.

This manual is based on a low level register access, and is written in such a manner to provide understanding to the user based on this type of access. If a driver is provided, please refer to the driver documentation for instruction using the higher level interface provided by the driver.

The part numbers covered by this manual are:

| Part Number   | Description                   |

|---------------|-------------------------------|

| 11027720-0001 | Direct Output only            |

| 11027720-0002 | Direct and Transformer Output |

® Registered Trademark of GreenSpring Computers

vi

# TABLE OF CONTENTS

| 1.0 GENERAL DESCRIPTION                   | 1   |

|-------------------------------------------|-----|

| 1.1 PURPOSE OF EQUIPMENT                  |     |

| 1.2 SPECIFICATIONS OF EQUIPMENT           | 1   |

| 1.2.1 Key Features                        |     |

| 1.2.2 Specifications                      |     |

| 1.2.3 Mechanical                          | 3   |

| 1.2.4 Environmental                       | 3   |

| 1.2.5 Bus Compliance                      | 4   |

| 1.2.6 Applicable Documents                |     |

| 2.0 INSTALLATION                          |     |

| 2.1 UNPACKING AND INSPECTION              | 5   |

| 2.2 HANDLING PRECAUTIONS                  | 5   |

| 2.3 INSTALLATION OF IP MODULES            | 5   |

| 2.4 PREPARATION FOR RESHIPMENT            | 6   |

| 3.0 FUNCTIONAL DESCRIPTION                | 7   |

| 3.1 GENERAL                               | 7   |

| 3.1.1 IP Interface                        | 7   |

| 3.1.2 Microcontroller                     | 7   |

| 3.1.3 Digital/Analog Converters (DACs)    | 7   |

| 3.1.4 Voltage Controlled Oscillator (VCO) | 8   |

| 3.1.5 Output Control                      |     |

| 3.1.6 Active Feedback                     |     |

| 3.1.7 Transformer                         | 8   |

| 3.2 OPERATION                             | 9   |

| 3.2.1 Operational Modes                   | 9   |

| 3.2.2 Output Level Control                | 10  |

| 3.2.3 Duty Cycle                          | 10  |

| 3.3 HARDWARE CONFIGURATION                | 11  |

| 3.4 CONNECTORS                            | 12  |

| 3.4.1 IP Logic Bus Connector              | 12  |

| 3.4.2 I/O Connector                       | 12  |

| 3.5 CONFIGURATION REGISTERS               | 13  |

| 3.5.1 ID PROM Registers                   | 13  |

| 3.5.2 I/O Registers                       | 13  |

|                                           |     |

| APPENDIX A - CONNECTORS                   | A-1 |

# LIST OF FIGURES

| Figure 1. IP Installation                                | 5   |

|----------------------------------------------------------|-----|

| Figure 2. Functional Block Diagram                       |     |

| Figure 3. Hardware Configurable Controls                 | 11  |

| Figure 4. I/O Registers                                  | 15  |

| Figure A-1. IP/Carrier Interface Connector Configuration | A-1 |

| Figure A-2. IP I/O Connector Configuration               | A-1 |

# LIST OF TABLES

| Table I. II | D PROM Contents          | 13 |

|-------------|--------------------------|----|

| Table II. I | I/O Address Map          | 13 |

|             | Frequency and Slew Rates |    |

#### **1.0 GENERAL DESCRIPTION**

The IP202S is a single wide industry pack (IP) function generator that provides a signal output that can sweep through a frequency range at a programmable slew rate. The output signal can be a sine, square, triangle, or sawtooth waveform up to 1 MHz. Signal amplitude and offset level can also vary with the frequency. The IP202S can be used with any conforming industry pack carrier module, such as VME/VXI, PXI, PC-AT, PCI, or cPCI.

## 1.1 PURPOSE OF EQUIPMENT

This IP is well suited for typical signal function generation and situations requiring frequency sweeping operations, such as the simulation of wheel sensor and tachometer outputs. The IP is particularly useful for testing automotive electronics, such as those used in anti-lock braking systems.

## **1.2 SPECIFICATIONS OF EQUIPMENT**

## 1.2.1 Key Features

- Slewable frequency with selectable frequency ranges

- Programmable slew (sweep) times, start/stop frequencies, amplitude, offset level, and dwell (delay) times

- Selectable waveform output -- sine, square, triangle, and sawtooth (sawtooth obtained by adjusting duty cycle of triangle waveform)

- Separately programmable output amplitude (10Vpp) and offset level (±5V) for both the start and stop frequencies

- Programmable and Externally Modulated Duty Cycle

- Fixed, Single Ramp, Single Cycle and Continuous Cycle modes

- External slew start synchronization using IP Strobe input or external strobe signal

- Software control to pause, then continue ramping or cycling

- Optional isolated transformer coupled output (-0002 option)

# 1.2.2 Specifications

## MAXIMUM RATINGS

| Parameter                 | Condition              | Rating     | Units |

|---------------------------|------------------------|------------|-------|

| Operating Temperature     |                        | +0 to +50  | °C    |

| Non-Operating Temperature |                        | -40 to +70 | °C    |

| Humidity                  | non-condensing         | 5 to 95    | %     |

| Power Consumption         | +5V from IP interface  | 150        | mA    |

|                           | +12V from IP interface | 60         | mA    |

|                           | -12V from IP interface | 60         | mA    |

# AC CHARACTERISTICS

|                                  |                                                  |      | Limit |                   |         |

|----------------------------------|--------------------------------------------------|------|-------|-------------------|---------|

| Parameter                        | Conditions                                       | Min  | Тур.  | Мах               | Units   |

| Frequency                        |                                                  |      |       |                   |         |

| - Range                          | Four sweep ranges <sup>1</sup>                   | 0    |       | 1.023             | MHz     |

| - Programming Resolution         | Range: 0 to 1.023KHz                             |      | 1     |                   | Hz      |

|                                  | 0 to 10.23KHz                                    |      | 10    |                   | Hz      |

|                                  | 0 to 102.3KHz                                    |      | 100   |                   | Hz      |

|                                  | 0 to 1.023MHz                                    |      | 1000  |                   | Hz      |

| - Accuracy                       | For frequencies > 1% of range full-scale         |      |       | 1.0               | %       |

| Direct Output Characteristics (C | OUT)                                             |      |       |                   |         |

| Output Impedance                 | Output enabled                                   | 0.5  |       | 1.0               | Ω       |

|                                  | Output disabled                                  |      | 180   |                   | ΚΩ      |

| Output Current                   |                                                  | -50  |       | +50               | mA      |

| Amplitude Range                  | No load                                          | 0    |       | 10                | Vpp     |

| Amplitude Resolution             | 8 bits                                           |      | 0.039 |                   | V       |

| Amplitude Accuarcy               | or 100mV, which ever is greater                  |      |       | ±7                | %       |

| DC Offset Range                  | No load                                          | -5   |       | +5                | V       |

| DC Offset Resolution             | 8 bits                                           |      | 0.039 |                   | V       |

| DC Offset Accuracy               | or 100mV, which ever is greater                  |      |       | ±7                | %       |

| Total Harmonic Distortion        | Sine wave                                        | -30  |       |                   | dB      |

| Rise/Fall Time                   | Square wave (10% to 90% at full output)          |      |       | 40                | ns      |

| Overshoot                        | No load, p-p amplitude at full output            |      |       | 2                 | %       |

| Transformer Output Characteris   | stics (TOUTH/L) (-0002 only)                     |      | •     | •                 | •       |

| Impedance                        | 10K:10K Transformer                              |      | 1     |                   | KΩ      |

| Response                         | 300Hz – 50KHz                                    |      | ±2    |                   | dB      |

| Frequency Sweep                  |                                                  | 1    | 1     |                   |         |

| Modes                            | Fixed, single ramp, single cycle, and continuous |      |       |                   |         |

| Туре                             | Exponential                                      |      |       |                   |         |

| Sweep Rate                       | Range: 0 to 1.023KHz                             | .020 |       | 6 <sup>2</sup>    | KHz/sec |

|                                  | 0 to 10.23KHz                                    | .2   |       | 60 <sup>2</sup>   | KHz/sec |

|                                  | 0 to 102.3KHz                                    | 2    |       | 600 <sup>2</sup>  | KHz/sec |

|                                  | 0 to 1.023MHz                                    | 20   |       | 6000 <sup>2</sup> | KHz/sec |

| Resolution                       | Incremental percentage change (7 bits)           |      | 5     |                   | %       |

#### **AC CHARACTERISTICS (continued)**

|                 |                                                   | Limit |      |      |       |

|-----------------|---------------------------------------------------|-------|------|------|-------|

| Parameter       | Conditions                                        | Min   | Тур. | Max  | Units |

| Amplitude Sweep |                                                   |       |      |      |       |

| Туре            | Linear                                            |       |      |      |       |

| Time            | Proportional to frequency sweep rate <sup>3</sup> |       |      |      |       |

| Span            |                                                   | 0     |      | 10   | Vpp   |

| DC Offset Sweep |                                                   |       |      |      |       |

| Туре            | Linear                                            |       |      |      |       |

| Time            | Proportional to frequency sweep rate <sup>3</sup> |       |      |      |       |

| Span            |                                                   | -5    |      | +5   | V     |

| Dwell Time      |                                                   |       |      |      |       |

| Resolution      | Programmable: 1ms, 10ms, 100ms, or 1 sec.         |       |      |      |       |

| Accuracy        | Percentage + 500µs                                |       | ±1   |      | %     |

| Duty Cycle      |                                                   |       |      |      |       |

| Resolution      | 5 bits                                            |       | 2.3  |      | %     |

| Range           |                                                   | 15    |      | 85   | %     |

| Accuracy        | In absolute percentage points                     |       | ±3   |      | %     |

| EXTSTB Input    |                                                   |       |      |      |       |

| Level           | Selectable: Zero Crossing                         |       | 0    |      | V     |

|                 | TTL                                               |       | 0.8  |      | V     |

|                 | CMOS                                              |       | 2.5  |      | V     |

| Input Impedance | Selectable: Low                                   |       | 50   |      | Ω     |

|                 | High                                              | 10    |      |      | KΩ    |

| EXTDC Input     |                                                   |       |      |      |       |

| Level           | Varies duty cycle from 85% down to 15%            | -2.3  |      | +2.3 | V     |

| Resolution      |                                                   |       | 15   |      | %/V   |

| Modulation      |                                                   |       |      | 2    | MHz   |

Notes:

1. All ranges start at 0Hz. Frequency ramping and cycling operations can not cross from one range to the next.

2. Although the values can be programmed higher than this, the practical limit is shown.

3. Point A to Point B in the same time frequency sweeps from Point A to Point B.

#### 1.2.3 Mechanical

The mechanical dimensions of the module are in conformance with ANSI/VITA 4-1995 for single-wide IP modules. The nominal dimensions are  $3.900^{\circ}$  (990.6 mm) long  $\times 1.800^{\circ}$ (4.572 mm) wide.

#### 1.2.4 Environmental

The environmental specifications of the module are:

| Operating Temperature: | $0^{\circ}C$ to $+50^{\circ}C$ |

|------------------------|--------------------------------|

| Storage Temperature:   | -40°C to +70°C                 |

| Humidity:              | <95% without condensation      |

Carrier modules may differ in environmental specification. Refer to the carrier's documentation for information.

# 1.2.5 Bus Compliance

The module complies with the Industry Pack Specification ANSI/VITA 4-1995 for single-wide IPs.

| Manufacturer ID: | 25 <sub>16</sub>                             |

|------------------|----------------------------------------------|

| Model Number:    | 02 <sub>16</sub>                             |

| Clock Rate:      | 8 MHz                                        |

| Data Transfer:   | 16 bit                                       |

| Strobe:          | supported                                    |

| Interrupts:      | not supported                                |

| DMA:             | not supported                                |

| ID Space:        | Twelve (12) bytes, including CRC (read-only) |

| IO Space:        | Four (4) 16-bit locations                    |

| Memory Space:    | none                                         |

# 1.2.6 Applicable Documents

ANSI/VITA 4-1995 Industry Pack Specification, VITA, 1995

#### 2.0 INSTALLATION

#### 2.1 UNPACKING AND INSPECTION

In most cases the IP202S is individually sealed and packaged for shipment. Verify that there has been no damage to the shipping container. If damage exists then the container should be retained as it will provide evidence of carrier caused problems. Such problems should be reported to the carrier immediately as well as to C&H. If there is no damage to the shipping container, carefully remove the module from its box and anti static bag and inspect for any signs of physical damage. If damage exists, report immediately to C&H.

#### 2.2 HANDLING PRECAUTIONS

The IP202S contains components that are sensitive to electrostatic discharge. When handling the module for any reason, do so at a static-controlled workstation, whenever possible. At a minimum, avoid work areas that are potential static sources, such as carpeted areas. Avoid unnecessary contact with the components on the module.

#### 2.3 INSTALLATION OF IP MODULES

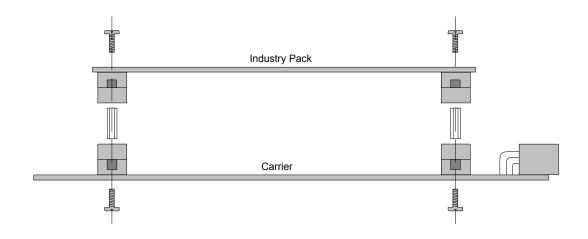

All IP modules must be installed into the carrier before the carrier is installed into the host system. IPs are installed by firmly pressing the connector on the IP together with the connector on the carrier. The connectors are keyed to prevent wrong insertion. Secure the IP with mounting hardware provided as shown in Figure 1.

Figure 1. IP Installation

#### 2.4 PREPARATION FOR RESHIPMENT

If the module is to be shipped separately it should be enclosed in a suitable water and vapor proof anti static bag. Heat seal or tape the bag to insure a moisture-proof closure. When sealing the bag, keep trapped air volume to a minimum.

The shipping container should be a rigid box of sufficient size and strength to protect the equipment from damage. If the module was received separately from a C&H system, then the original module shipping container and packing material may be re-used if it is still in good condition.

#### **3.0 FUNCTIONAL DESCRIPTION**

#### 3.1 GENERAL

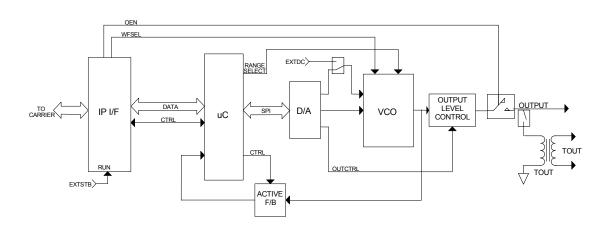

The IP202S provides a signal output that can sweep through a frequency range at a programmable slew rate. The output signal can be a sine, square, triangle, or sawtooth waveform up to 1 MHz. A simplified block diagram of the module is shown in Figure 2.

Figure 2. Functional Block Diagram

## 3.1.1 IP Interface

The IP interface provides the electrical connection, buffering, and control between the carrier board and the frequency generation and slewing logic.

#### 3.1.2 Microcontroller

The microcontroller provides timing of all functions for slew rate control of the output frequency. Serial data is continuously output to the digital/analog converters to set the VCO at the desired frequency and duty cycle.

#### 3.1.3 Digital/Analog Converters (DACs)

These serial DACs convert the serial data from the microcontroller into a voltage level signal to control the VCO.

3.1.4 Voltage Controlled Oscillator (VCO)

The VCO converts the voltage input from the DACs into a output signal of the desired frequency, duty cycle, and waveform.

#### 3.1.5 Output Control

The output control provides output amplitude control and signal conditioning.

#### 3.1.6 Active Feedback

The active feedback logic provides continuous output frequency monitoring and input to the microcontroller for frequency adjustment due to temperature and component variations.

#### 3.1.7 Transformer

The optional transformer coupled output provides an magnetically isolated signal source for loads requiring isolation from the module ground. The frequency response is 300Hz - 50KHz ( $\pm 2$ dB). The reflected source impedance is 1000 ohms. The DC Offset capability is lost due to the transformer coupling.

#### 3.2 OPERATION

#### 3.2.1 Operational Modes

Four modes of operation are available: Fixed, Single Ramp, Single Cycle, and Continuous Cycle. The mode of operation is controlled by configuration bits in the Status/Control Register. In all modes, the RUN bit must be set to allow frequency sweeping. The STB (Strobe Enable) bit, allows external hardware synchronization of the beginning of the cycle. With Strobe enabled, in Single Ramp and Single Cycle modes, the strobe signal acts as a trigger. The ramp or cycle begins when the strobe signal goes active and will complete the ramp or cycle regardless of the level of the strobe signal. In Fixed or Continuous Cycle mode, the output frequency will follow or start cycling when the strobe signal goes active. When the strobe signal goes inactive, it will hold at the current frequency. However, if it becomes active again, the output will change to and start from Frequency A.

<u>Fixed Mode</u> In Fixed mode, the output frequency slews to the programmed Frequency A at the rate specified by Slew Rate A. If the programmed Frequency A is changed, the output frequency slews toward the new programmed value at the specified slew rate. If the programmed frequency is changed before the frequency is reached, the output frequency slews from the current frequency towards the new programmed frequency at the specified slew rate. Dwell Times A and B are ignored in this mode.

<u>Single Ramp</u> In Single Ramp mode, the output frequency always begins at Frequency A. The cycle begins when the RUN bit is set. If the current frequency is not equal to Frequency A, the output frequency immediately changes (ignoring the slew rate) to the programmed Frequency A. The output then slews toward Frequency B at the rate specified by Slew Rate A. When Frequency B is reached, the RUN bit is automatically cleared and the output frequency holds at Frequency B. The output amplitude and offset level also changes according to the programmed values for Amplitude A and B and Offset A and B (see 3.2.2). Dwell Times A and B are ignored in this mode.

<u>Single Cycle</u> In Single Cycle mode, the output frequency always begins at Frequency A. The cycle begins when the RUN bit is set. If the current frequency is not equal to Frequency A, the output frequency immediately changes (ignoring the slew rate) to the programmed Frequency A. The output then slews toward Frequency B at the rate specified by Slew Rate A. When Frequency B is reached, the output remains at Frequency B until Dwell Time B has expired. It then slews toward Frequency A at the rate specified by Slew Rate B. When Frequency A is reached, the RUN bit is automatically cleared and the output frequency holds at Frequency A. The output amplitude and offset level also changes according to the programmed values for Amplitude A and B and Offset A and B (see 3.2.2). Dwell Time A is ignored in this mode.

<u>Continuous Cycle</u> Continuous Cycle mode operates the same as Single Cycle mode, except operation does not stop after one cycle and the RUN bit is not cleared. The output frequency continuously sweeps between Frequency A and Frequency B. When Frequency B is reached, the output remains at Frequency B until Dwell Time B has expired. It then slew towards Frequency A at the rate specified by Slew Rate B. When Frequency A is reached, the output remains at Frequency A until Dwell Time A has expired and then the cycle repeats. The

output amplitude and offset level also change according to the programmed values for Amplitude A and B and Offset A and B (see 3.2.2).

## 3.2.2 Output Level Control

The output level is controlled by setting the Amplitude and Offset in the Output Level Control Register. The amplitude and offset for Frequency A can be different than the Frequency B amplitude and offset. During frequency slewing, the amplitude and offset will proportionally change as the frequency changes. The peak-to-peak amplitude can be varied from 0Vpp to 10Vpp and the DC offset can be varied from -5V to +5V. To output a waveform with a low level of 0V and a high level of 4V, set the amplitude to 4Vpp and the offset to +2V.

## 3.2.3 Duty Cycle

The waveform duty cycle (defined as the percentage of time that the output waveform is above the DC offset) can be software programmed or controlled by an external signal to facilitate pulse-width modulation and the generation of sawtooth waveforms. The duty cycle can also be used to reduce sine-wave distortion. The Duty Cycle jumper as described in section 3.3 defines the method of control. The duty cycle can vary from 15% to 85%. To software program the duty cycle, place the Duty Cycle jumper in the SW position and program the desired duty cycle in the Status/Control Register. To control the duty cycle externally, place the Duty Cycle jumper in the EXT position and apply a -2.3V to +2.3V signal to the EXTDC control pin on the IP I/O connector. The duty cycle can be modulated up to 2MHz.

#### 3.3 HARDWARE CONFIGURATION

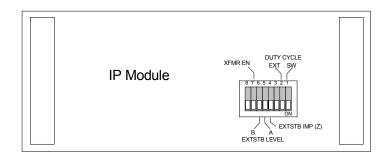

Jumper selectable options are shown in Figure 3.

Figure 3. Hardware Configurable Controls

XFMR EN This switch enables the optional transformer coupled output.

<u>Duty Cycle</u> These switches select either software or external duty cycle control to allow generation of sawtooth waveforms or pulse-width modulation of the output signal. Do not select both.

EXTSTB Impedance (Z) This switch selects the input impedance of the EXTSTB front connector signal. With the switch ON the input impedance is  $50\Omega$ . With the switch OFF (default), the impedance is >10K $\Omega$ .

<u>EXTSTB Level</u> These switches control the threshold level of the EXTSTB front connector signal. The level can be set to 0V (zero crossing), TTL (0.8V), or CMOS (2.5V).

|           | Switch |     |  |

|-----------|--------|-----|--|

| Threshold | Α      | В   |  |

| 0V        | OFF    | OFF |  |

| TTL       | ON     | ON  |  |

| CMOS      | ON     | OFF |  |

# 3.4 CONNECTORS

## 3.4.1 IP Logic Bus Connector

The IP logic bus connector contains signal and voltage connections for the standard IP interface logic. (See Appendix A for pin assignments)

## 3.4.2 I/O Connector

The IP I/O connector provides the output signal and various status/control signals. (See Appendix A for pin assignments)

| OUT     | Sine, triangle, or square wave signal out (Variable Level Output and Offset)                                                                                                                                                                                                                                                                                                              |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TOUTH   | Isolated transformer coupled output, high side (1000Q, 300Hz-50KHz response)                                                                                                                                                                                                                                                                                                              |

| TOUTL   | Isolated transformer coupled signal output, low side (1000 \OVER, 300 Hz-50 KHz response)                                                                                                                                                                                                                                                                                                 |

| EXTSTB* | The External Strobe is logically ORed (either strobe active produces an internal Strobe signal) with the IP interface STROBE* signal to produce the internal Strobe signal. A 10K pull-up is provided on the EXTSTB*. <i>(TTL/CMOS Active Low Input)</i>                                                                                                                                  |

| EXTDC   | The External Duty Cycle adjust input controls the waveform duty cycle (defined as a percentage of time the waveform is positive) if the Duty Cycle jumper is configured for external duty cycle control. Varying the voltage from $+2.3V$ to $-2.3V$ causes the output duty cycle to vary from 15% to 85%, about 15% per volt. The duty cycle can be modulated up to 2MHz. <i>(Input)</i> |

| +5V     | +5V supply. Can used for external buffer, amplifier, or other logic. (Do not exceed 500mA)                                                                                                                                                                                                                                                                                                |

| +12V    | +12V supply. Can used for external buffer, amplifier, or other logic. (Do not exceed 100mA)                                                                                                                                                                                                                                                                                               |

| -12V    | -12V supply. Can used for external buffer, amplifier, or other logic. (Do not exceed 100mA)                                                                                                                                                                                                                                                                                               |

#### 3.5 CONFIGURATION REGISTERS

#### 3.5.1 ID PROM Registers

The ID PROM registers provide manufacturer and module number as shown in Table I.

| IP Address, hex | Register Description              | Value, hex |

|-----------------|-----------------------------------|------------|

| 01              | ASCII "I"                         | 49         |

| 03              | ASCII "P"                         | 50         |

| 05              | ASCII "A"                         | 41         |

| 07              | ASCII "C"                         | 43         |

| 09              | Manufacturer ID                   | 25         |

| 0B              | Model Number                      | 02         |

| 0D              | Revision Level                    | 10*        |

| 0F              | Reserved                          | 00         |

| 11              | Low Byte Driver ID (Firmware Rev) | 30*        |

| 13              | High Byte Driver ID               | 00         |

| 15              | Number of Bytes Used              | 0C         |

| 17              | CRC                               | 84*        |

Table I. ID PROM Contents

\* These values may differ, depending on the revision levels.

#### 3.5.2 I/O Registers

There are a variety of registers used to configure and control the IP202S module. The registers are addressable within the I/O Space. An address map of the registers is shown in Table II. Details of the registers is provided in Figure 4.

| IO Address, hex | Register Description     |

|-----------------|--------------------------|

| 00              | Status/Control           |

| 02              | Waveform Control         |

| 04              | Output Amplitude Control |

| 06              | Output Offset Control    |

| 08              | Frequency A Control      |

| 0A              | Dwell/Slew A Control     |

| 0C              | Frequency B Control      |

| 0E              | Dwell/Slew B Control     |

Table II. I/O Address Map

<u>Status/Control Register</u>  $(00_{16})$  This read/write register provides the main control and status of the module operation Bits are provided for controlling the operational mode, strobe (run) configuration, output enable, and self-test initiation.

<u>Waveform Control Register</u>  $(02_{16})$  This read/write register provides control of the waveform (square, triangle, or sine), duty cycle, and frequency range.

<u>Output Amplitude Control Register</u>  $(04_{16})$  This read/write register provides control of the peakto-peak signal level of the output at Frequency A and at Frequency B. <u>Output Offset Control Register</u>  $(06_{16})$  This read/write register provides control of the voltage offset of the output at Frequency A and at Frequency B.

<u>Frequency A/B Control</u>  $(08_{16}/0C_{16})$  These read/write registers provides control of Frequency A and B. A special read-back mode on the Frequency A Register allows the current output frequency to be monitored. The output frequency and resolution depends on the Range selected in the Waveform Control Register as shown in Table III.

<u>Dwell/Slew A/B Control</u>  $(0A_{16}/0E_{16})$  These read/write registers provides control of the dwell time and slew rate for Frequency A and B. Dwell A sets the amount of time the output stays (dwells) at Frequency A after either Run is enabled or Frequency A is reached when in Continuous Cycle mode. Slew A sets the rate at which the output frequency will sweep from Frequency B after Frequency B. Dwell B sets the amount of time the output stays (dwells) at Frequency B after Frequency B is reached when in Single Cycle or Continuous Cycle mode. Slew B sets the rate at which the output frequency B to Frequency A. Table III shows the slew rate range for each frequency range. Each increment in slew rate is 5% faster than the previous slew rate. The following formulas apply:

if SlewValue =  $7F_{16}$ , then SlewRate =  $\infty$  (frequency change is immediate), else SlewRate =  $20 \times RangeFactor \times 1.05^{SlewValue}$

$$SlewValue = \frac{\log\left(\frac{SlewRate}{20 \times RangeFactor}\right)}{\log(1.05)}$$

where SlewRate = the desired slew rate in Hz/second SlewValue = the 7-bit binary register value for the slew RangeFactor = the multiply factor for the selected range:  $\frac{Selected Range}{0 - 1.020 \text{KHz}} = \frac{Factor}{1}$

| 0 1.02011112 | -    |

|--------------|------|

| 0 - 10.20KHz | 10   |

| 0 - 102.0KHz | 100  |

| 0 - 1.020MHz | 1000 |

|                | Frequency Bit |                        | Slew Rate     |

|----------------|---------------|------------------------|---------------|

| Selected Range | Resolution    | Slew Rate Range        | Resolution    |

| 0 - 1.023KHz   | 1Hz           | 20 - ~10K Hz/sec.      | 5% increments |

| 0 - 10.23KHz   | 10Hz          | 200 - ~100K Hz/sec.    | 5% increments |

| 0 - 102.3KHz   | 100Hz         | $2K - \sim 1M$ Hz/sec. | 5% increments |

| 0 - 1.023MHz   | 1000Hz        | 20K - ~10M Hz/sec.     | 5% increments |

Table III. Frequency and Slew Rates

#### **Status/Control Register**

| 00    |    |          |        |    |    |     |     |    |     |   |      |   |     |     |     |     |  |

|-------|----|----------|--------|----|----|-----|-----|----|-----|---|------|---|-----|-----|-----|-----|--|

| Bit   | 15 | 14       | 13     | 12 | 11 | 10  | 9   | 8  | 7   | 6 | 5    | 4 | 3   | 2   | 1   | 0   |  |

| Write |    | (read-   | only)  |    | -  | RBI | FCO | RS | PAU |   | Mode |   | INV | STB | RUN | OEN |  |

| Read  |    | Selftest | Result |    | -  | RBI | FCO | RS | PAU |   | Mode |   | INV | STB | RUN | OEN |  |

*RBI*  $\Rightarrow$  Read-back Information Select (0 = default, 1 = factory use only)

- *FCO*  $\Rightarrow$  Frequency Correction Off (0 = default, 1 = factory use only)

- $RS^1 \Rightarrow Run Selftest (1 = run selftest, cleared when selftest is completed)$

- PAU  $\Rightarrow$  Pause (0 = normal, 1 = pause sweeping)

- Mode  $\Rightarrow$  Slew Mode

- 0 0 0 Fixed (follows Freq. A)

- 0 0 1 Single Ramp (from Freq. A to Freq. B and hold)

- 0 1 0 Single Cycle (from Freq. A to Freq. B then back to Freq. A and hold)

- 0 1 1 Continuous Cycle (cycle between Frequency A and B)

- 1 X X (reserved)

- INV  $\Rightarrow$  Invert External Strobe (0 = active low, 1 = active high)

- $STB^2 \Rightarrow$  Strobe Enable (0 = ignore strobe, 1 = use strobe signal to control sweeping)

- RUN  $\Rightarrow$  Run/Stop (1 = run, 0 = hold a current frequency<sup>3</sup>)

- OEN  $\Rightarrow$  Output Enable (0 = disabled, 1 = enabled)

- Selftest Result ⇔ Selftest Result (0 = successful, 1 = failure, Bit 12=1KHz range, Bit 13=10KHz range, Bit 14=100KHz range, Bit 15=1MHz range, reset on register read)

#### Notes:

00

- 1) Output is temporarily disabled during selftest.

- 2) When STB is set to 1, in Single Ramp and Single Cycle modes, the strobe signal acts as a trigger. The ramp or cycle begins when the strobe signal goes active and will complete the ramp or cycle regardless of the level of the strobe signal. In Fixed or Continuous Cycle mode, the output frequency will follow or start cycling when the strobe signal goes active. When the strobe signal goes inactive, it will hold at the current frequency. However, if it becomes active again, the output will change to and start from Frequency A. In either case, the RUN bit must also be set for STB to control operation.

- 3) When RUN is set to 0, the output holds at the current frequency, but will change to and start from Frequency A when the RUN bit is set back to a 1.

|       |    |    |    |    |    | ****    | CIULI | $\mathbf{m} \mathbf{c} \mathbf{v}$ | IIII U | LINUG | 19101 |     |   |   |   |    |

|-------|----|----|----|----|----|---------|-------|------------------------------------|--------|-------|-------|-----|---|---|---|----|

| 02    |    |    |    |    |    |         |       |                                    |        | c     |       |     |   |   |   |    |

| Bit   | 15 | 14 | 13 | 12 | 11 | 10      | 9     | 8                                  | 7      | 6     | 5     | 4   | 3 | 2 | 1 | 0  |

| Write | -  | -  | -  |    | D  | uty Cyc | le    |                                    | -      | -     | Ra    | nge | - | - | W | FS |

| Read  | -  | 1  | -  |    | D  | uty Cyc | le    |                                    | -      | 1     | Ra    | nge | 1 | - | W | FS |

Waveform Control Register

Duty Cycle  $\Rightarrow$  Waveform Duty Cycle ( $00_{16} = 85\%$ ,  $1F_{16} = 15\%$ , resolution is ~2.3% per bit, default =  $0F_{16} = \sim 50\%$ )

|         | - 10        |                |

|---------|-------------|----------------|

| Range □ | > Frequence | y Range Select |

|         | 0 0         | 0 - 1.023KHz   |

|         | 0 1         | 0 - 10.23KHz   |

|         | 1 0         | 0 - 102.3Khz   |

|         | 11          | 0 - 1.023MHz   |

| WFS =   | > Wavefor   | m Select       |

|         | 0 0         | Square wave    |

|         | 0 1         | Triangle wave  |

|         | 1 X         | Sine wave      |

|         |             |                |

Figure 4. I/O Registers

|       |    |    |    |       | Out    | put A | Ampl | itud | e Coi | itrol | Reg | ister |        |   |   |   |

|-------|----|----|----|-------|--------|-------|------|------|-------|-------|-----|-------|--------|---|---|---|

| 04    |    |    |    |       |        |       |      |      |       |       | 8   |       |        |   |   |   |

| Bit   | 15 | 14 | 13 | 12    | 11     | 10    | 9    | 8    | 7     | 6     | 5   | 4     | 3      | 2 | 1 | 0 |

| Write |    |    |    | Ampli | tude B |       |      |      |       |       |     | Ampli | tude A |   |   |   |

| Read  |    |    |    | Ampli | tude B |       |      |      |       |       |     | Ampli | tude A |   |   |   |

Amplitude A/B  $\Rightarrow$  Output Peak-to-Peak Amplitude for Frequency A or B ( $00_{16} = 0V$ , FF<sub>16</sub> = +10V, ~0.04V per bit (default =  $00_{16}$ ))

|       |    |    |    |      | 0     | utpu | t Off | fset ( | Contr | ol R | egist | er   |       |   |   |   |

|-------|----|----|----|------|-------|------|-------|--------|-------|------|-------|------|-------|---|---|---|

| 06    |    |    |    |      |       | -    |       |        |       |      | 0     |      |       |   |   |   |

| Bit   | 15 | 14 | 13 | 12   | 11    | 10   | 9     | 8      | 7     | 6    | 5     | 4    | 3     | 2 | 1 | 0 |

| Write |    |    |    | Offs | set B |      |       |        |       |      |       | Offs | set A |   |   |   |

| Read  |    |    |    | Offs | set B |      |       |        |       |      |       | Offs | set A |   |   |   |

Offset A/B  $\Rightarrow$  Output Offset Voltage for Frequency A or B ( $00_{16} = -5V$ ,  $80_{16} = 0V$ , FF<sub>16</sub> = +5V, ~0.04V per bit (default =  $80_{16}$ ))

Figure 4. I/O Registers (continued)

| 08    |     | (not used) Programmed Frequency A                                 |    |          |    |    |   |   |   |       |        |        |       |   |   |   |

|-------|-----|-------------------------------------------------------------------|----|----------|----|----|---|---|---|-------|--------|--------|-------|---|---|---|

| Bit   | 15  | 14                                                                | 13 | 12       | 11 | 10 | 9 | 8 | 7 | 6     | 5      | 4      | 3     | 2 | 1 | 0 |

| Write | RBM |                                                                   | (1 | 10t used | )  |    |   |   |   |       | Freque | ency A |       |   |   |   |

| Read  | 0   |                                                                   | (1 | 10t used | l) |    |   |   |   | Progr | ammed  | Freque | ncy A |   |   |   |

| Read  | 1   | (not used) Programmed Frequency A<br>(not used) Current Frequency |    |          |    |    |   |   |   |       |        |        |       |   |   |   |

#### **Frequency A Control Register**

RBM  $\Rightarrow$  Read-Back Mode (0 = read programmed value, 1 = read current frequency) Frequency A  $\Rightarrow$  Desired Frequency A. See 3.2.1 for details.

Note: The data read in the Frequency A bits depends on the read-back mode (RBM) selected.

#### **Dwell/Slew Rate A Control Register**

| 011   |    |    |    |    |         |        |   |   |   |   |   |     |        |     |   |   |

|-------|----|----|----|----|---------|--------|---|---|---|---|---|-----|--------|-----|---|---|

| Bit   | 15 | 14 | 13 | 12 | 11      | 10     | 9 | 8 | 7 | 6 | 5 | 4   | 3      | 2   | 1 | 0 |

| Write | DF | RA |    |    | Dwell ' | Time A |   |   | - |   |   | Sle | w Valu | e A |   |   |

| Read  | DF | RA |    |    | Dwell   | Time A |   |   | - |   |   | Sle | w Valu | e A |   |   |

DR A  $\Rightarrow$  Dwell Time Range

0A

- 0 0 Milliseconds

- 0 1 Tens of milliseconds

- 1 0 Hundreds of milliseconds

- 1 1 Seconds

Dwell Time A ⇒ Amount of time (value × Dwell Time Range) the output stays (dwells) at Frequency A before sweeping to Frequency B. See 3.5.2 for details.

Slew Value A  $\Rightarrow$  Rate of change for ramping from Frequency A to Frequency B. See 3.5.2 for details.

#### Figure 4. I/O Registers (continued)

|       |     |    |    |          | -  | 1040 | i vii v | $\mathbf{P} \mathbf{v}$ | onu |       | SIDUC   |          |       |   |   |   |

|-------|-----|----|----|----------|----|------|---------|-------------------------|-----|-------|---------|----------|-------|---|---|---|

| 0C    |     |    |    |          |    | -    | ·       |                         |     |       | U       |          |       |   |   |   |

| Bit   | 15  | 14 | 13 | 12       | 11 | 10   | 9       | 8                       | 7   | 6     | 5       | 4        | 3     | 2 | 1 | 0 |

| Write | RBM |    | (1 | not used | i) |      |         |                         |     |       | Freque  | ency B   |       |   |   |   |

| Read  | 0   |    | (1 | 10t used | l) |      |         |                         |     | Progr | ammed   | Freque   | ncy B |   |   |   |

| Read  | 1   |    | (1 | not used | i) |      |         |                         |     | (1    | factory | use only | y)    |   |   |   |

#### **Frequency B Control Register**

RBM  $\Rightarrow$  Read-Back Mode (0 = read programmed value, 1 = factory use only) Frequency B  $\Rightarrow$  Desired Frequency B. See 3.2.1 for details.

Note: The data read in the Frequency B bits depends on the read-back mode (RBM) selected.

#### **Dwell/Slew Rate B Control Register**

| 0E    |    |    |    |    |       |        |   |   |   |   | - 8 |     |        |     |   |   |

|-------|----|----|----|----|-------|--------|---|---|---|---|-----|-----|--------|-----|---|---|

| Bit   | 15 | 14 | 13 | 12 | 11    | 10     | 9 | 8 | 7 | 6 | 5   | 4   | 3      | 2   | 1 | 0 |

| Write | DR | RВ |    |    | Dwell | Time B |   |   | - |   |     | Sle | w Valu | e B |   |   |

| Read  | DR | RВ |    |    | Dwell | Time B |   |   | - |   |     | Sle | w Valu | e B |   |   |

DR B  $\Rightarrow$  Dwell Time Range

0 0 Milliseconds

0 1 Tens of milliseconds

1 0 Hundreds of milliseconds

1 1 Seconds

Dwell Time B ⇒ Amount of time (value × Dwell Time Range) the output stays (dwells) at Frequency B before sweeping to Frequency A. See 3.5.2 for details.

Slew Value B  $\Rightarrow$  Rate of change for ramping from Frequency B to Frequency A. See 3.5.2 for details.

#### Figure 4. I/O Registers (continued)

| I/O Pin | Signal | I/O Pin | Signal   |

|---------|--------|---------|----------|

| 1       | GND    | 26      | GND      |

| 2       | CLK    | 27      | +5V      |

| 3       | RESET- | 28      | R/W-     |

| 4       | D0     | 29      | IDSEL-   |

| 5       | D1     | 30      | DMAREQ0- |

| 6       | D2     | 31      | MEMSEL-  |

| 7       | D3     | 32      | DMAREQ1- |

| 8       | D4     | 33      | INTSEL-  |

| 9       | D5     | 34      | DMACK0-  |

| 10      | D6     | 35      | IOSEL-   |

| 11      | D7     | 36      | reserved |

| 12      | D8     | 37      | A1       |

| 13      | D9     | 38      | DMAEND-  |

| 14      | D10    | 39      | A2       |

| 15      | D11    | 40      | ERROR-   |

| 16      | D12    | 41      | A3       |

| 17      | D13    | 42      | INTREQ0- |

| 18      | D14    | 43      | A4       |

| 19      | D15    | 44      | INTREQ1- |

| 20      | BS0-   | 45      | A5       |

| 21      | BS1-   | 46      | STROBE-  |

| 22      | -12V   | 47      | A6       |

| 23      | +12V   | 48      | ACK-     |

| 24      | +5V    | 49      | reserved |

| 25      | GND    | 50      | GND      |

# **APPENDIX A - CONNECTORS**

Figure A-1. IP/Carrier Interface Connector Configuration

| I/O Pin | Signal  | I/O Pin | Signal |

|---------|---------|---------|--------|

| 1       | GND     | 26      | GND    |

| 2       |         | 27      |        |

| 3       | GND     | 28      |        |

| 4       | OUT     | 29      | GND    |

| 5       | GND     | 30      |        |

| 6       |         | 31      | GND    |

| 7       | GND     | 32      |        |

| 8       | TOUTH   | 33      |        |

| 9       | GND     | 34      |        |

| 10      | TOUTL   | 35      |        |

| 11      | GND     | 36      |        |

| 12      | EXTSTB- | 37      | GND    |

| 13      | GND     | 38      |        |

| 14      | EXTDC   | 39      | GND    |

| 15      |         | 40      |        |

| 16      |         | 41      |        |

| 17      |         | 42      |        |

| 18      |         | 43      |        |

| 19      |         | 44      |        |

| 20      |         | 45      |        |

| 21      |         | 46      |        |

| 22      | -12V    | 47      |        |

| 23      | +12V    | 48      |        |

| 24      | +5V     | 49      |        |

| 25      | GND     | 50      | GND    |

Figure A-2. IP I/O Connector Configuration

NOTES:

#### **READER'S COMMENT FORM**

Your comments assist us in improving the usefulness of C&H's publications; they are an important part of the inputs used for revision.

C&H Technologies, Inc. may use and distribute any of the information that you supply in any way that it believes to be appropriate without incurring any obligation whatsoever. You may, of course, continue to use the information which you supply.

Please refrain from using this form for technical questions or for requests for additional publications; this will only delay the response. Instead, please direct your technical questions to your authorized C&H representative.

COMMENTS:

Thank you for helping C&H to deliver the best possible product. Your support is appreciated.

Sincerely,

F.R.Harrison President and CEO

#### **INSTRUCTIONS**

In its continuing effort to improve documentation, C&H Technologies, Inc. provides this form for use in submitting any comments or suggestions that the user may have. This form may be detached, folded along the lines indicated, taped along the loose edge (DO NOT STAPLE), and mailed. Please try to be as specific as possible and reference applicable sections of the manual or drawings if appropriate. Also, indicate if you would like an acknowledgment mailed to you stating whether or not your comments were being incorporated.

NOTE: This form may not be used to request copies of documents or to request waivers, deviations, or clarification of specification requirements on current contracts. Comments submitted on this form do not constitute or imply authorization to waive any portion of the referenced document(s) or to amend contractual requirements.

— (Fold along this line) —

(Fold along this line) —

Place Stamp Here

C&H Technologies, Inc. Technical Publications P. O. Box 14765 Austin, Texas 78761-4765