# $U \ S \ E \ R \ ' \ S \quad M \ A \ N \ U \ A \ L$

INTELLIGENT PXI CARRIER

> MODEL VX407C

Document Part No: 11028564

## **COPYRIGHT**

C&H Technologies, Inc. (C&H) provides this manual "as is" without warranty of any kind, either expressed or implied, including but not limited to the implied warranties of merchantability and fitness for a particular purpose. C&H may make improvements and/or changes in the product(s) and/or program(s) described in this manual at any time and without notice.

This publication could contain technical inaccuracies or typographical errors. Changes are periodically made to the information herein; these changes will be incorporated in new editions of this publication.

# Copyright © 2003 by C&H Technologies, Inc.

The information and/or drawings set forth in this document and all rights in and to inventions disclosed herein which might be granted thereon disclosing or employing the materials, methods, techniques or apparatus described herein, are the exclusive property of C&H Technologies, Inc.

A Reader's Comment Form is provided at the back of this publication. If this form has been removed address comments to:

C&H Technologies, Inc. Technical Publications 445 Round Rock West Drive Austin, Texas 78681-5012

Or visit our web site for support information at:

http://www.chtech.com.

C&H may use or distribute any of the information you supply in any way that it believes appropriate without incurring any obligations.

## **MODULE WARRANTY**

C&H Technologies, Inc. warrants its modules to be free from defects in material and workmanship for three years from date of shipment. C&H will repair or replace the defective product without charge within the warranty period, provided the defective item is shipped, freight prepaid, to C&H Technologies, 445 Round Rock West Drive, Round Rock, Texas 78681. C&H will pay return freight charges to any point in the continental United States or Canada.

Obligations under this warranty shall be limited to repair or replacement, at C&H's discretion, of any product or part thereof which has been returned by the original purchaser with transportation prepaid and, upon examination by C&H, found to be defective. C&H assumes no responsibility for loss or damage to equipment being returned for repair or replacement under the terms of this warranty. Equipment which, upon examination by C&H, requires repair or replacement of parts thereof as a result of improper installation, misuse, unauthorized alterations or repairs, or user negligence, will have such repairs or replacement of parts made at then current rates.

This warranty does not cover damage caused by misuse, neglect, accident, or improper application or installation. C&H shall not be liable for consequential damages of any kind arising out of the purchase, installation, use or misuse of the product. C&H makes no representation or warranty of any kind, either expressed or implied, with respect to equipment operation or procedures. Any action that the user may take in reliance upon the operation or accuracy of this equipment shall be taken solely at the user's own responsibility and risk.

Please notify the C&H sales department to obtain a Return Authorization Number (RAN) prior to return of a product under the terms of this warranty. Notification is to include the Model and Serial numbers of the product along with full details of the problem. Modules returned should clearly show the RAN on the outside of the package.

# AMENDMENT NOTICE

C&H Technologies, Inc. makes every attempt to provide up-to-date manuals with the associated equipment. Occasionally, changes are made to the equipment wherein it is necessary to provide amendments to the manual. If any amendments are provided for this manual they are printed on colored paper and will be provided with the module and manual. Manual updates may also be found on out web site at www.chtech.com.

# **NOTE**

The contents of any amendment may affect operation, maintenance, or calibration of the equipment.

# **INTRODUCTION**

This manual describes the operation and use of the C&H Model VX407C Intelligent PXI/cPCI Carrier Module (Part Number 11028580). This VXI module is one of a number of test and data acquisition/control modules in the VME and VXI format provided by C&H.

Contained within this manual are the physical and electrical specifications, installation and startup procedures, functional description, and configuration guidelines to adequately use the product.

The part numbers covered by this manual are:

| Part Number   | <u>Description</u>        |

|---------------|---------------------------|

| 11028580-0001 | VX407C Single Wide Module |

| 11028580-0002 | VX407C Double Wide Module |

| 11028580-0003 | VX407C Triple Wide Module |

# TABLE OF CONTENTS

| 1.0 | GEN.       | ERAL DES      | SCRIPTION                      | 1    |

|-----|------------|---------------|--------------------------------|------|

|     | 1.1        | <b>PURPOS</b> | E OF EQUIPMENT                 | 1    |

|     | 1.2        | SPECIFIC      | CATIONS OF EQUIPMENT           | 1    |

|     |            |               | Key Features                   |      |

|     |            | 1.2.2         |                                |      |

|     |            | 1.2.3         | Electrical                     | 2    |

|     |            | 1.2.4         | Mechanical                     | 3    |

|     |            | 1.2.5         | Environmental                  | 3    |

|     |            | 1.2.6         | Bus Compliance                 | 4    |

| 2.0 | INST       | ALLATIO       | N                              | 5    |

|     | 2.1        | UNPACK        | ING AND INSPECTION             | 5    |

|     | 2.2        |               | NG PRECAUTIONS                 |      |

|     | 2.3        | INSTALI       | LATION OF PXI/CPCI MODULES     | 5    |

|     | 2.4        |               | LATION OF PMC MODULES          |      |

|     | 2.5        | INSTALI       | LATION OF VX407C CARRIER       | 7    |

|     | 2.6        | PREPAR.       | ATION FOR RESHIPMENT           | 7    |

| 3.0 | <b>FUN</b> | CTIONAL       | OVERVIEW                       | 8    |

|     | 3.1        | GENERA        | L                              | 8    |

|     | 3.2        | HARDW         | ARE OVERVIEW                   | 8    |

|     |            | 3.2.1         | PXI/cPCI Modules               | 9    |

|     |            | 3.2.2         | Shared Memory                  | 9    |

|     |            | 3.2.3         | PowerPC and Peripherals        |      |

|     |            | 3.2.4         | VXI Interface Logic            |      |

|     |            | 3.2.5         | PMC Slot                       | . 10 |

|     |            | 3.2.6         | External Drivers               | . 10 |

|     |            | 3.2.7         | JTAG/COP Interface             | . 11 |

|     | 3.3        | SOFTWA        | RE OVERVIEW                    | . 11 |

|     | 3.4        | HARDW         | ARE CONFIGURATION              | . 11 |

|     |            | 3.4.1         | Logical Address Switch         | . 12 |

|     |            | 3.4.2         | Module Configuration Switch    | . 13 |

|     |            | 3.4.3         | PowerPC Configuration Switches | . 14 |

|     |            | 3.4.4         | VIO Configuration Jumper       | . 16 |

|     |            | 3.4.5         | PPBV Configuration Jumper      | . 17 |

|     | 3.5        |               | CTORS                          |      |

|     |            | 3.5.1         | External Power Connectors.     | . 17 |

|     |            | 3.5.2         | External Drivers Connector     | . 18 |

|     |            | 3.5.3         | JTAG/COP Connector             | . 18 |

|     |            | 3.5.4         | PMC Connectors                 | . 18 |

|     |            | 3.5.5         | PMC I/O Connector              | . 18 |

|     |            | 3.5.6         | VXI Connectors                 | . 18 |

|     |            | 3.5.7         | PXI/cPCI Connectors            | . 18 |

| 4.0 | SYST       | TEM ARCI      | HITECTURE                      | . 19 |

|     | 4.1        |               | EW                             |      |

|     | 4.2        | DEVICE-       | SIDE ARCHITECTURE              | . 19 |

|     |            | 4.2.1         | PowerPC Memory Map             | . 20 |

|     |            | 4.2.2         | SDRAM                          | . 22 |

|            |      | 4.2.3   | Boot RC  | )M                             | 22 |

|------------|------|---------|----------|--------------------------------|----|

|            |      | 4.2.4   | Flash M  | emory                          | 22 |

|            |      | 4.2.5   | PCIbus . | Architecture                   | 22 |

|            |      |         | 4.2.5.1  |                                |    |

|            |      |         | 4.2.5.2  | IDSEL Signal Routing           |    |

|            |      |         | 4.2.5.3  | PCI Interrupts                 |    |

|            |      |         | 4.2.5.4  | Shared Memory Device           |    |

|            |      |         | 4.2.5.5  | PXI/cPCI Devices               |    |

|            |      |         |          | PMC Device                     |    |

|            |      | 4.2.6   |          |                                |    |

|            |      | 4.2.7   |          | ons Registers                  |    |

|            |      | 4.2.8   |          | Drivers                        |    |

|            |      | 4.2.9   |          | OP Interface                   |    |

|            | 4.3  |         |          | HITECTURE                      |    |

|            | ч.5  |         |          | mory Map                       |    |

|            |      | 4.3.2   |          | s Width                        |    |

|            |      | 4.3.3   |          | Mastering and Direct Access    |    |

|            | 4.4  |         |          | RCES AND DEVICE COMMUNICATIONS |    |

|            | 4.4  | 4.4.1   |          | ons Registers                  |    |

|            |      | 4.4.1   |          | VXI Configuration Registers    |    |

|            |      |         |          |                                |    |

|            |      |         |          | VXI Communication Registers    |    |

|            |      | 4.4.2   |          | VX407C Control Registers       |    |

|            |      | 4.4.2   |          | ord Serial Protocol            |    |

|            |      | 4.4.3   |          | Purpose Shared Memory          |    |

|            |      |         |          | Shared Memory Arbitration      |    |

|            |      | 4 4 4   | 4.4.3.2  | DMA/Burst                      |    |

|            |      | 4.4.4   |          | sage Unit                      |    |

| <b>5</b> 0 | COET | 4.4.5   |          | Purpose FIFOs                  |    |

| 5.0        |      |         |          | TURE                           |    |

|            | 5.1  |         |          | OFTWARE                        |    |

|            | 5.2  |         |          | EM UTILITIES                   |    |

|            |      | 5.2.1   | -        | Resource Usage                 |    |

|            |      |         | _        | ration Options                 |    |

|            |      | 5.2.3   |          | ation Routines                 |    |

|            |      |         |          | PowerPC Initialization         |    |

|            |      |         |          | PCIbus Enumeration             |    |

|            |      |         |          | Power-On-Self-Test (POST)      |    |

|            |      |         |          | Launching the Application      |    |

|            |      |         |          | ord Serial Protocol Handler    |    |

|            |      | 5.2.5   | IEEE 48  | 8.2 Utilities                  | 53 |

|            |      | 5.2.6   | System   | Calls                          | 56 |

|            |      | 5.2.7   | System   | Commands                       | 57 |

|            | 5.3  |         |          | ON                             |    |

| 6.0        | PROC | GRAMMIN | NG INSTE | RUCTIONS                       | 60 |

|            | 6.1  | MAKING  | SYSTEN   | M CALLS                        | 60 |

|            | 6.2  | FLASH P | ROGRAN   | MMING                          | 60 |

|            | 6.3  | PCI ACC | ESSES    |                                | 61 |

|            | 6.4  | FIRMWA  | RE DOW   | NLOAD                          | 62 |

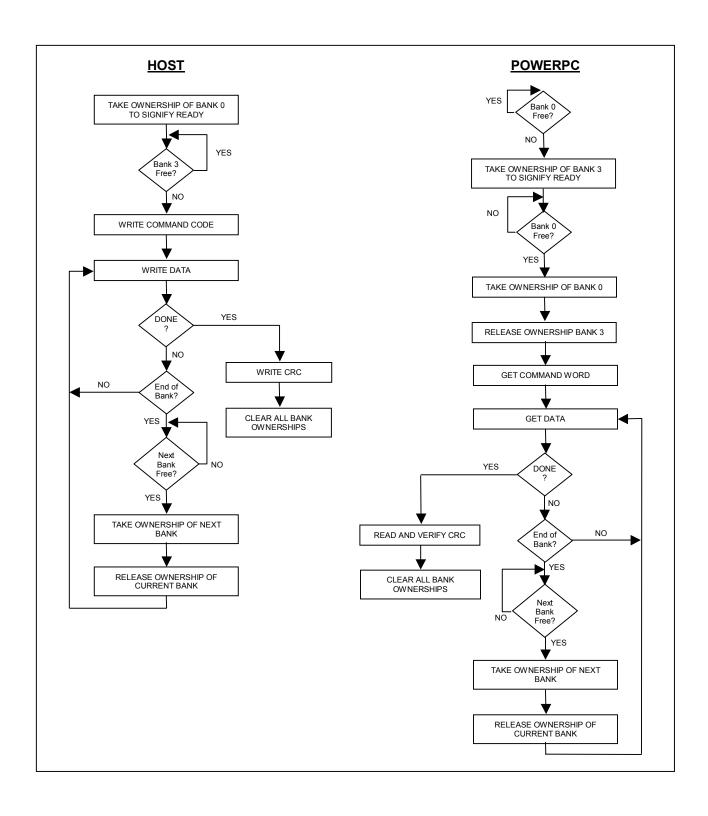

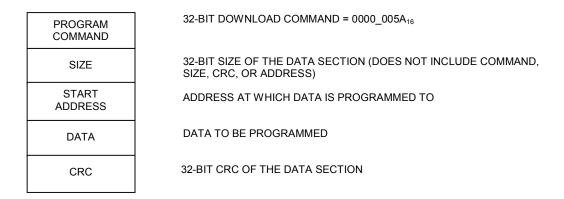

|         | 6.4.1     | Firmwa   | re Download Mode Protocol             | 62  |

|---------|-----------|----------|---------------------------------------|-----|

|         | 6.4.2     | Downlo   | ad Commands                           | 65  |

|         |           | 6.4.2.1  | Generic Download Command              | 65  |

|         |           | 6.4.2.2  | Flash Program Command                 | 65  |

|         | 6.4.3     |          | ector Erase Command                   |     |

|         |           | 6.4.3.1  | Boot Command                          | 67  |

| 6.5     | INTERRU   | JPTS     |                                       | 67  |

|         | 6.5.1     | PCI Inte | errupts                               | 68  |

|         |           |          | errupts                               |     |

| 6.6     | CONFIG    | URING T  | RIGGERS                               | 69  |

| 6.7     | VXI WOI   | RD SERIA | AL COMMUNICATIONS                     | 70  |

|         | 6.7.1     | User Co  | mmand Interpreter                     | 70  |

| 6.8     | HOST-SI   | DE PCI E | BUS MASTERING AND DIRECT ACCESS       | 72  |

|         |           | 6.8.1.1  | PCI Configuration Accesses            | 73  |

|         |           | 6.8.1.2  | Byte Enables in a Direct Access Cycle | 73  |

| APPEND: | IX A CON  | NECTOR   | S                                     | A-1 |

| APPEND: | IX B CON  | FIGURAT  | ΓΙΟΝ REGISTERS                        | B-1 |

| APPEND: | IX C SYST | EM CAL   | LS                                    | C-1 |

| APPEND: | IX D SYST | EM CON   | MMANDS                                | D-1 |

# LIST OF FIGURES

| Figure 1 Front Panel and Top View (Top Shield Not Shown)  | 6   |

|-----------------------------------------------------------|-----|

| Figure 2 PMC Module Installation                          |     |

| Figure 3 System Hardware Architecture                     | 9   |

| Figure 4 Hardware Layout.                                 |     |

| Figure 5 Logical Address Configuration Switch             | 13  |

| Figure 6 Module Configuration Switch                      |     |

| Figure 7 PowerPC Configuration Switches                   |     |

| Figure 8 VIO Configuration Jumper                         |     |

| Figure 9 PPBV Configuration Jumper                        |     |

| Figure 10 Device-Side Architecture                        |     |

| Figure 11 Address Map Overview                            |     |

| Figure 12 Detailed PowerPC Address Map                    | 21  |

| Figure 13 Shared Memory Organization                      |     |

| Figure 14 Trigger Architecture                            |     |

| Figure 15 External Driver Control Register                |     |

| Figure 16 Host-Side Architecture                          |     |

| Figure 17 VXI Memory Organization                         |     |

| Figure 18 Shared Resources                                |     |

| Figure 19 VXI Configuration Registers                     |     |

| Figure 20 VXI Communications Registers                    |     |

| Figure 21 VX407C Control Registers                        |     |

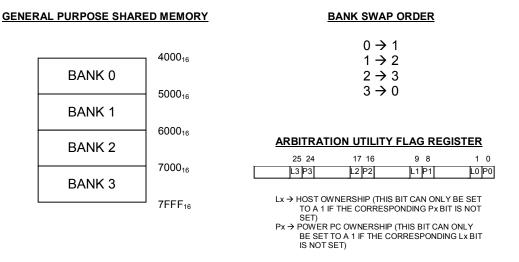

| Figure 22 Shared Memory Arbitration Utility Flag Register | 41  |

| Figure 23 General Purpose FIFO Registers                  |     |

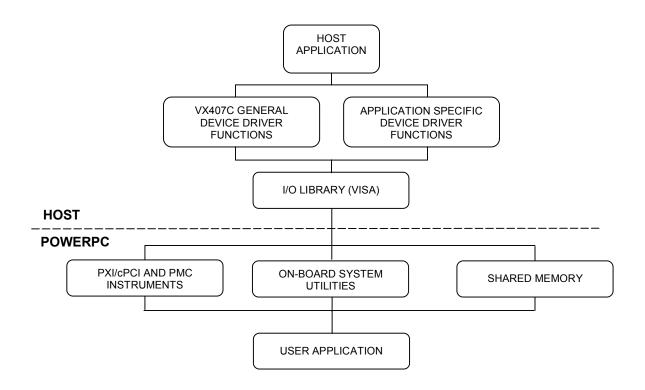

| Figure 24 System Software Architecture                    |     |

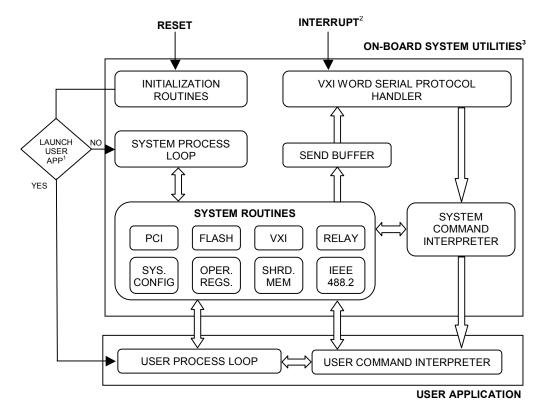

| Figure 25 On-board System Utilities Software Architecture |     |

| Figure 26 System Resource Usage                           | 47  |

| Figure 27 IEEE 488.2 Status Report Model                  |     |

| Figure 28 System Call Example Code                        |     |

| Figure 29 Shared memory banks for firmware update         |     |

| Figure 30 Firmware Update Protocol                        |     |

| Figure 31 Generic Download Command                        |     |

| Figure 32 Flash Program Command                           | 66  |

| Figure 33 Flash Sector Erase Command                      | 67  |

| Figure 34 Boot Command                                    |     |

| Figure 35 User Command Interpreter Example Code           |     |

| Figure 36 Direct Access Control Register                  |     |

|                                                           |     |

| Figure A-1 PXI/CPCI Slot B P1 (P1B) Pin Configuration     | A-1 |

| Figure A-2 PXI/CPCI Slot B P2 (P2B) Pin Configuration     | A-1 |

| Figure A-3 PXI/CPCI Slot A P1 (P1A) Pin Configuration     | A-2 |

| Figure A-4 PXI/CPCI Slot A P2 (P2A) Pin Configuration     |     |

| Figure A-5 VXI P1 Pin Configuration                       |     |

| Figure A-6 VXI P2 Pin Configuration                       | A-4 |

| Figure A-7 PMC Pin Configuration                          |     |

| Figure A-8 PMC Pin Configuration (continued)              |     |

| Figure A-9 External Driver Outputs (J4)                   |     |

| Figure A-10 JTAG/COP Header (J1)          | A-7 |

|-------------------------------------------|-----|

| Figure A-11 External Power Connectors     | A-7 |

| Figure A-12 PMC I/O Connector             | A-7 |

|                                           |     |

| LIST OF TABLES                            |     |

| Table I PowerPC Configuration Signals     | 16  |

| Table II IDSEL Signal Routing             | 24  |

| Table III PCI Interrupt Signal Routing    | 24  |

| Table IV Operations Registers Map         |     |

| Table V Configuration Options             |     |

| Table VI IEEE 488.2 Common Commands       |     |

| Table VII System Calls                    | 57  |

| Table VIII System Commands                |     |

| Table B-1 PowerPC Configuration Registers | B-1 |

| Table C-1 System Calls                    |     |

| Table D-1 System Commands                 |     |

| Table D-2 IEEE 488.2 Common Commands      |     |

|                                           |     |

## 1.0 GENERAL DESCRIPTION

The VX407C is an intelligent VXI carrier that allows PXI and CompactPCI (cPCI) modules to be used in VXI systems. The carrier supports two 3U or one 6U PXI or cPCI modules. It features an on-board PowerPC processor that can perform command translation, data analysis, and many other data processing or process control functions.

# 1.1 PURPOSE OF EQUIPMENT

The VX407C was designed for Automated Test Equipment (ATE) applications requiring on-board instrument intelligence or data processing. Some of the more common applications include: legacy instrument emulation, data intensive signal acquisition and control, high speed signal analysis, and control processing.

# 1.2 SPECIFICATIONS OF EQUIPMENT

# 1.2.1 Key Features

- 300MHz Motorola MPC8245 Integrated Processor

- □ Two 33 MHz, 5V or 3.3V PXI/cPCI slots

- One 33 MHz, 5V or 3.3V PMC slot

- □ 128 megabytes P133 SDRAM

- 16 kilobytes dual-ported SRAM accessible by both the processor and VXI

- 8 megabytes flash memory

- Message based or register based VXI interface

- VXI A24/A32 access to shared memory

- VXI block transfers to/from shared memory

- DMA transfers between PowerPC, PCI devices and shared memory

- Direct access to PXI/cPCI and PMC modules from VXI

- On-board system utilities supports application development

- Supports common off-the-shelf real-time operating systems

## 1.2.2 Specifications

#### **Processor:**

- Motorola 300MHZ MPC8245

- MPC603e core

- 16KB/16KB L1 Integrated Cache

#### **Local PCI Bus:**

• 33MHZ 32-bit

#### **Main Memory:**

- 128MB SDRAM

- 8MB Flash, VXI programmable

- 32KB Boot ROM, socketed

#### **Shared Memory:**

- 16 KB Dual-ported SRAM

- Four 32 deep 32-bit FIFO's

- DMA/Burst support

- Internal arbitration

- Fully accessible by both VXI and PowerPC

#### cPCI/PXI Interface:

- Two 3U modules or one 6U module

- 33MHz 32-bit

- PXI triggers map to VXI TTL triggers

- cPCI/PXI interrupt to PowerPC supported

- On-board PXI CLK10 source

## **PMC** Interface:

- Support for one PMC module

- IEEE P1386.1 32-bit compliant

- 33MHz 32-bit

- PMC I/O connected to 64-pin header

#### **External Relay Control:**

- Darlington relay driver, 8-channels

- Controlled by PowerPC

- 5V 500mA (single channel)

- 16-pin header

#### **Interrupts:**

- PCI to PowerPC interrupt support

- PowerPC to VXI interrupt level 1-7 (programmable)

- VXI Host to PowerPC interrupt support

#### **Temperature:**

Operating: 0°C to 50°C Storage: -40°C to 70°C

#### **Direct Access:**

- Direct VXI access of cPCI/PXI modules

- Up to 8K of local PCI address space can be directly mapped to VXI A24 or A32 space

#### **Debugging Interface:**

- Common On-Chip Processor (COP)/JTAG

- Standard COP header

- Third-party development tools supported

#### **On-Board System Utilities:**

- Boot-up and initialization

- VXI word serial protocol support

- Firmware download to Flash memory via VXI

- PCI bus enumeration

#### **RTOS Support:**

Architecture supports common real-time operating systems, such as VxWorks, OS-9, Linux, and others.

#### 1.2.3 Electrical

The VX407C requires the +5V, ±12V, and ±24V power from the VXI back plane. The +5V supply drives a DC to DC converter supplying +3.3V to carrier components and the PXI/cPCI and PMC positions. The VXI backplane can provide a total of 7.2 amps of +5 volts, of which, the VX407C uses a maximum of 2.3 amps (11.5W) for internal purposes. The remaining 4.9 amps (24W) are available to the PXI/cPCI and PMC through a combination of the +5V and +3.3V supplies. Of that 4.9 amps, a maximum of 4.4 amps (14.5W) can be provided via the +3.3V supply.

The  $\pm 12$  volt supply is not used internally by the carrier, but may be required by an installed PXI/cPCI or PMC module. The carrier can provide up to 1.5 amps (18W) each of both +12 volts and -12 volts to the PXI/cPCI and PMC positions.

The  $\pm 24$ V is neither used by the carrier nor the PXI/cPCI and PMC modules. However, it is available at an external connector for special purpose use. The carrier can supply a maximum of 1 amp (24W) each to the +24V and the -24V pins on the connector.

An external connection to the +5V supply is also provided. A maximum of 2.5 amps (12.5W) can be sourced or sink-ed to/from the carrier. As an output, the power drawn from this connector reduces the total power available to the PXI/cPCI and PMC positions. As an input, the power provided to this connector increases the available power to the PXI/cPCI and PMC positions. Even with an external +5V source an absolute maximum of 6 amps of +5 volts and 4.4 amps of +3.3 volts can be provided to the PXI/cPCI and PMC positions.

For electrical information on individual PXI/cPCI modules, please reference each module's documentation. The power requirements for each PXI/cPCI or PMC module installed must be added to the VX407C's requirements for the total module's requirements.

#### 1.2.4 Mechanical

The mechanical dimensions of the VX407C are in conformance with the VXI bus specification for the height and width of Size-C modules. The nominal dimensions are 233.35 mm (9.187 in) high x 189.0 mm (7.441 in) deep. With the shield and a PXI/cPCI module installed, the total dimensions are 233.35 mm (9.187 in) high x 340.0 mm (13.386 in) deep. The module is designed for a standard mainframe with 30.48 mm (1.2 in) width between slots. The double-wide option is 60.96 mm (2.4 in) wide and will occupy two slots. The triple wide option is 91.44 mm (3.6 in) wide and will occupy three slots.

# 1.2.5 Environmental

The environmental specifications of the module are:

Operating Temperature: 0°C to +50°C Storage Temperature: -40°C to +70°C

Humidity: <95% without condensation

# 1.2.6 Bus Compliance

The module complies with the VXIbus Specification Revision 1.4 for C-Size VXI modules and with VMEbus Specification ANSI/IEEE STD 1014-1987, IEC 821.

Manufacturer ID: FC1<sub>16</sub> (can also be set by PowerPC)

Model Code: FE4<sub>16</sub> (can also be set by PowerPC)

VXI Access Type: Register Based or Message Based

VXI Addressing: A16/A24/A32 VXI Data Transfer: D16/D32 VXI Sysfail: supported

VXI Interrupts: ROAK, programmable levels

VXI Local Bus: Available

TTL Triggers SYNC trigger protocol supported

Memory Requirements: 32 Kilobytes

The module's on-board PXI/cPCI bus complies with PCI Spec. 2.2 and PXI Spec. 2.0 for cPCI and PXI 3U or 6U modules.

PXI Bus Data Width: 32-bit PXI Bus Speed 33 MHz

PXI Bus Voltage 5V or 3.3V (jumper selectable)

PXI Triggers supported

PXI Clock 10 On-board 10MHz source

The modules on-board PMC bus complies with the PMC Specification IEEE P1386.1 for 32-bit PMC modules.

PMC Bus Data Width: 32-bit PMC Bus Speed 33 MHz

PMC Bus Voltage 5V or 3.3V (jumper selectable)

PMC I/O: 64-pin Header

## 2.0 INSTALLATION

# 2.1 UNPACKING AND INSPECTION

In most cases the VX407C is individually sealed and packaged for shipment. Verify that there has been no damage to the shipping container. If damage exists then the container should be retained as it will provide evidence of carrier caused problems. Such problems should be reported to the carrier immediately as well as to C&H. If there is no damage to the shipping container, carefully remove the module from its box and anti static bag and inspect for any signs of physical damage. If damage exists, report immediately to C&H.

## 2.2 HANDLING PRECAUTIONS

The VX407C contains components that are sensitive to electrostatic discharge. When handling the module for any reason, do so at a static-controlled workstation, whenever possible. At a minimum, avoid work areas that are potential static sources, such as carpeted areas. Avoid unnecessary contact with the components on the module.

#### 2.3 INSTALLATION OF PXI/cPCI MODULES

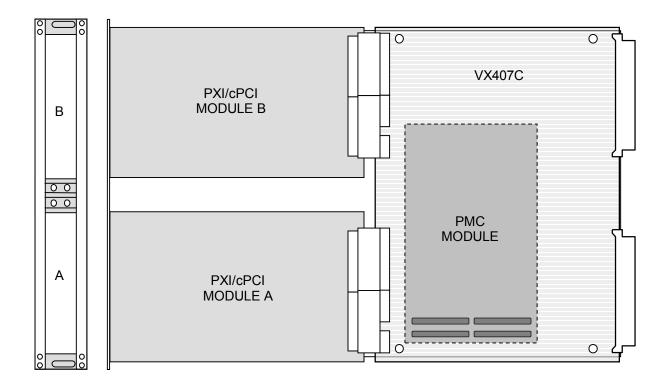

PXI/cPCI modules must be installed before the VX407C is installed into the VXI system. To install modules, remove the VX407C's top shield and front panel covers as needed. *There is never a need to remove the VX407C's bottom shield.* Install PXI/cPCI modules by carefully sliding the module through the opening in the front panel of the VX407C and firmly pressing the connector on the PXI/cPCI module together with the connector on the carrier.

There are two mounting locations on the carrier: A and B. 3U PXI/cPCI modules may be installed into either location. 6U modules must be installed into location A. The mounting locations are illustrated in Figure 1.

WARNING: For most VXI systems it is required to remove the injector/ejector of the PXI/cPCI module in slot A. The guide pin on the PXI/cPCI injector/ejector prevents the module from properly fitting in most VXI chassis.

Figure 1 Front Panel and Top View (Top Shield Not Shown)

# 2.4 INSTALLATION OF PMC MODULES

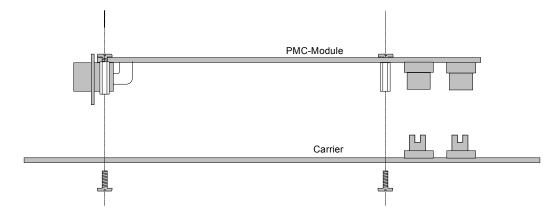

PMC modules must be installed into the carrier before the carrier is installed into the host system. To install modules, remove the VX407C's top shield. *There is never a need to remove the VX407C's bottom shield.* Firmly press the connector on the PMC module together with the connector on the carrier as shown in Figure 2. Secure the module through the holes in the bottom shield using the original screws.

**Figure 2 PMC Module Installation**

## 2.5 INSTALLATION OF VX407C CARRIER

CAUTION: Read the entire User's Manual before proceeding with the installation and application of power.

If necessary, remove the top shield from the VX407C and configure the switches and jumpers. Set the module's logical address and addressing mode as described in section 3.4. Replace the shield and insert the carrier into the appropriate slot according to the desired priority and apply power. If no obvious problems exist, proceed to communicate with the module as outlined throughout the rest of this manual.

## 2.6 PREPARATION FOR RESHIPMENT

If the module is to be shipped separately it should be enclosed in a suitable water and vapor proof anti static bag. Heat seal or tape the bag to insure a moisture-proof closure. When sealing the bag, keep trapped air volume to a minimum.

The shipping container should be a rigid box of sufficient size and strength to protect the equipment from damage. If the module was received separately from a C&H system, then the original module shipping container and packing material may be re-used if it is still in good condition.

## 3.0 FUNCTIONAL OVERVIEW

## 3.1 GENERAL

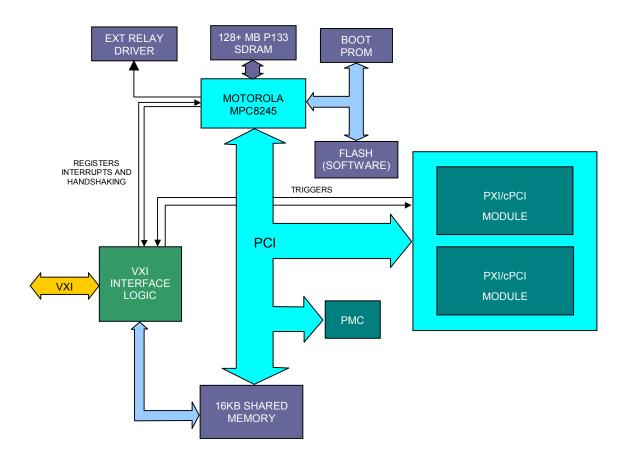

The VX407C provides an intelligent interface between the VXI bus and two 3U or one 6U PXI or CompactPCI(cPCI) modules. It features an embedded processor system powered by a Motorola MPC8245 integrated processor. The on-board PCI bus provides an interface to the two PXI/cPCI positions as well as one PMC module position and 16 kilobytes of shared memory. VXI interface logic provides an interface between the VXI bus and the PowerPC via the shared memory and the PowerPC's local bus.

The software architecture provides a flexible platform for the user applications to perform necessary tasks. On-board system utilities include: boot-up and initialization routines, system configuration routines, VXI communications routines, and various hardware interface routines to provide a basic interface to the carrier and installed PXI/cPCI modules and to assist application development. The system architecture also supports various commercially available real time operating systems.

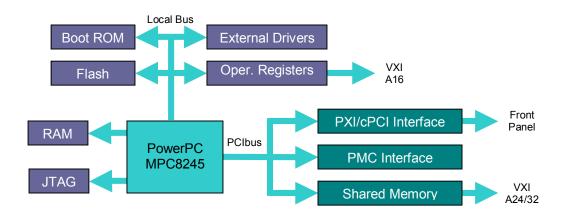

## 3.2 HARDWARE OVERVIEW

The VX407C is powered by a highly integrated Motorola MPC8245 microprocessor with a PowerPC 603e core, a built-in Peripheral Component Interconnect (PCI) interface, and an advanced memory controller. The processor along with flash memory, ROM memory, and SDRAM form a complete embedded processing system with all the peripherals necessary for flexible application development.

Dual-ported shared memory and VXI interface logic allow for seamless communication between the VXI host and the PowerPC. Interrupts and handshaking logic is also provided to assist communications between the host and PowerPC.

A single PMC positions and two PXI/cPCI positions allow a variety of instruments and peripherals to be added to the system. Both the VXI host and the PowerPC can communicate with and control the modules.

Finally, relay driver logic allows special control hardware to be easily added to the overall integrated system. Figure 3 illustrates the system hardware architecture.

Figure 3 System Hardware Architecture

## 3.2.1 PXI/cPCI Modules

The PXI/cPCI modules provide the measurement and control functionality for the given application. The carrier can support up to two 3U or one 6U PXI or CompactPCI (cPCI) modules. The modules can be controlled over the on-board PCI bus by both the PowerPC application and the VXI host via the shared memory device. A variety of modules are commercially available from numerous manufacturers.

# 3.2.2 Shared Memory

The 16 kilobyte shared memory device acts as a buffer between the VXI bus and the on-board PCI bus. The device provides 16 kilobytes of dual-port SRAM and various other communications utilities such as general purpose FIFO's. It connects to the VXI bus through a local bus interface controlled by the VXI interface logic and to the PowerPC through the PCI bus. The device performs on-chip memory arbitration allowing the 16 kilobytes of memory to be accessed at the same time from both the VXI bus and the

PowerPC. It also contains an embedded PCI bus controller allowing the VXI bus to directly access the on-board PCI bus and thus directly access the PXI/cPCI modules.

# 3.2.3 PowerPC and Peripherals

The PowerPC architecture was designed as a standard embedded processor system. It consists of a Motorola MPC8245 PowerPC, a boot ROM device, 128 megabytes of P133 SDRAM, and a flash memory device. This architecture allows the developer to select from standard off-the-shelf development tools and real-time operating systems for application development.

The PowerPC acts as the PCI bus master and can access both PXI/cPCI modules as well as the PMC module and the shared memory device. It also can access the VXI interface logic to perform handshaking between itself and the VXI bus.

## 3.2.4 VXI Interface Logic

The VXI interface logic acts as a transparent interface between the VXI bus and the shared memory device. It translates VXI bus accesses into shared memory local bus accesses by managing all local bus address and control lines. It maps all of the shared memory device's address space to VXI A24/A32 space.

The VXI interface also handles handshaking between the PowerPC and the VXI bus. It includes a set of registers that are mapped to VXI A16 space and are accessible by the PowerPC to handle host to device communications and handshaking.

Finally the interface logic provides VXI bus trigger and interrupt capabilities. The carrier has extensive mapping capabilities between the PXI trigger lines and the VXI bus trigger lines controllable by the VXI host. VXI interrupts can be generated by the PowerPC application on any of the 8 VXI interrupt levels.

## 3.2.5 PMC Slot

The PMC slot on the PCI bus can be used to add additional functionality not provided by the carrier. For example, a mass storage device could be added for on-board data collection by installing a PMC disk drive controller. The PMC position is accessible by both the PowerPC and the VXI host.

#### 3.2.6 External Drivers

The PowerPC can control a Darlington sink driver device residing on its local memory bus. The device's outputs are available at a 16 pin header for external use. The device is intended to drive external relays, display LED's, or other high current devices.

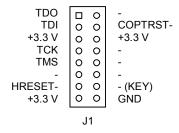

## 3.2.7 JTAG/COP Interface

The JTAG interface to the PowerPC provides a debug and development interface supported by many standard off-the-shelf developments tools. The interface is used by development tools to communicate with the processor. It provides the developer with the ability to view system registers, view memory, set breakpoints, and use other standard debugging practices.

#### 3.3 SOFTWARE OVERVIEW

The embedded software on the carrier as well as the host software are very application dependant and thus, must be developed specifically to suit the needs of the particular application. However, on-board system utilities are provided to assist application development and to provide basic functionality when no application exists.

When no application exists, the system software provides basic functionality allowing the user to communicate with the carrier and the PXI/cPCI and the PMC modules. A limited set of VXI message based commands are available as well as the ability to access all defined registers and the shared memory. In this capacity, the carrier can operate as a fully functional instrument without the existence of a user application.

If a user application is to be provided, the on-board system utilities assist the developer in performing several tasks that require advanced knowledge of the carrier architecture and the devices that make up that architecture. For example a system routine is provided to program the flash memory so that the developer does not need to refer to the flash device's data sheet to learn the programming protocol. Also, the on-board system utilities automatically handle the communications required for VXI message passing so that the application can concentrate on performing high level tasks and not on the details of the VXI word serial protocol. The on-board system utilities are completely independent and fully interrupt and exception driven so they only take up a very small amount of processor resources and so the user application can be independently compiled and linked without knowledge of the system utilities' memory organization.

# 3.4 HARDWARE CONFIGURATION

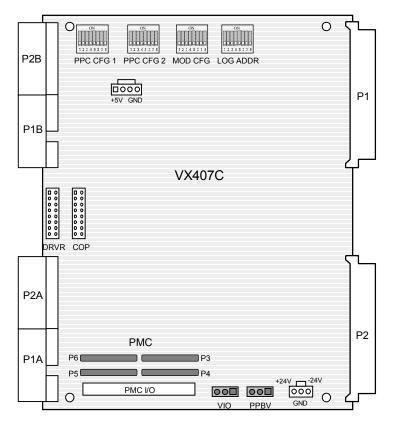

There are several switch and jumper selectable settings that configure the VX407C for operation. Configuration options include: the VXI logical address, PowerPC options, programming modes, and operational voltages. Figure 4 shows the layout of all the switches and jumpers on the VX407C.

Figure 4 Hardware Layout

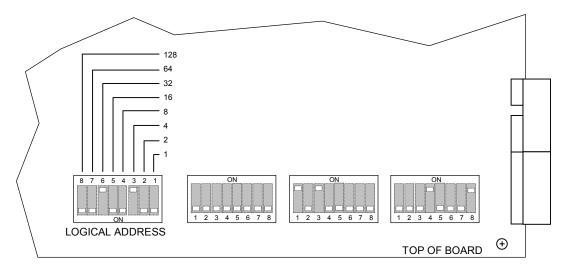

# 3.4.1 Logical Address Switch

The logical address switch specifies the logical address for the VX407C. The switches form a binary weighted decimal value that sets the logical address of the module. The OFF position for each switch represents a binary one in that bit position. For example, the switch settings shown in Figure 5 would result in a logical address of 36.

Figure 5 Logical Address Configuration Switch

# 3.4.2 Module Configuration Switch

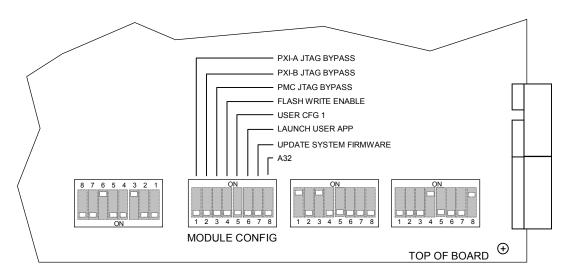

The module configuration switch is used to set some of the miscellaneous options on the VX407C. Figure 6 shows the options that are configurable with this switch.

Figure 6 Module Configuration Switch

JTAG Bypass Switches: These switches specify whether or not to bypass a PCI device's JTAG interface. The on-board JTAG bus is daisy chained between the PowerPC, the JTAG/COP debug header, the PXI devices, and the PMC device. The daisy chain must not be broken in order for JTAG operation to work correctly, including the JTAG debug operation. Therefore, if a PXI or PMC slot is vacant or the installed PXI or PMC device

does not provide the JTAG bypass, the corresponding switch must be set to ON as to not break the daisy chain.

<u>Flash Write Enable Switch</u>: This switch will enable or disable the ability for software to program flash memory. Setting this switch to ON will enable the flash programming capability. When the flash programming capability is disabled, the carrier configuration options cannot be modified. See section 5.2.2 for details on configuration options.

<u>User Configuration Switch</u>: The user configuration switch is available for use by a user application. The switch has not effect on the hardware operation of the VX407C. The value of the switch is copied to the operations registers so that the user application can read the value and use it however it wishes. Setting the switch to ON results in the corresponding bit of the operations register being set to a binary '0'.

<u>Launch User Application Switch</u>: This switch determines whether or not the initialization firmware will attempt to launch a user application or will launch the onboard system application. The on-board system application will allow the user to perform configuration routines and basic instrument communications. If this switch is set to OFF the firmware will attempt to launch the user application. Should a situation arise where the user application will not launch or the VX407C crashes on boot up this switch should be set to ON so basic configuration and debug can be performed.

<u>Update System Firmware Switch</u>: This switch puts the VX407C into a mode where the on-board system utilities can be updated. This is the only function that can be performed in this mode. If this switch is set to OFF at power-up, the carrier will go into the firmware update mode and wait for an update to complete. If this switch is ON at power-up, the carrier will initialize normally.

<u>A32 Switch</u>: This switch selects whether the VX407C performs VXI A24 or A32 address decoding. This address space is used to access the shared memory device. If this switch is set to ON, the carrier requests memory in the systems A32 address space, otherwise A24 address space is requested.

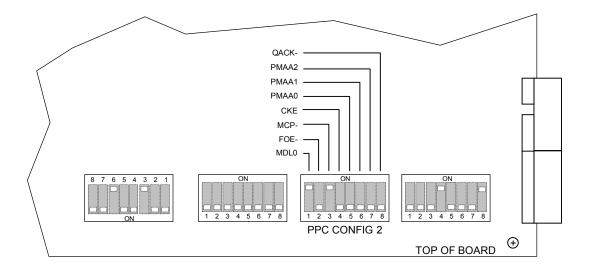

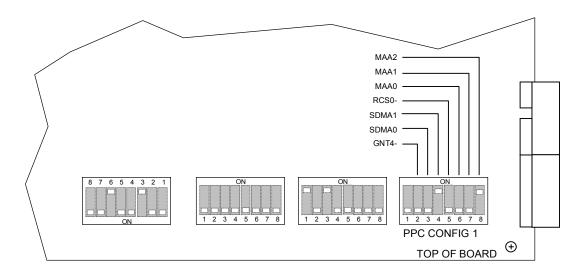

# 3.4.3 PowerPC Configuration Switches

The PowerPC configuration switches determine the value of the corresponding signals during reset. Each signal connected to these switches is a reset configuration signal for the PowerPC. The values of these signals at reset determine the configuration of the processor. Figure 7 shows all available PowerPC reset configuration options. Table I briefly describes each option and all possible settings. These switches are preset during manufacturing to the optimal settings for the VX407C. Modifying these settings is rarely necessary and in some cases may cause the VX407C to not function correctly. For details on reset configuration refer to the MPC8245 User's Manual.

**Figure 7 PowerPC Configuration Switches**

**Table I PowerPC Configuration Signals**

| Signal | Description                          | Settings                                                     |

|--------|--------------------------------------|--------------------------------------------------------------|

| MDL0,  | Selects the data bus width for ROM   | $(MDL0 = 0, FOE_ = 0) = ROM 32$ -bit, SDRAM 32-bit           |

| FOE-   | bank 0 and SDRAM                     | $(MDL0 = 0, FOE_{=} = 1) = ROM 8-bit, SDRAM 32-bit^{1,2}$    |

|        |                                      | (MDL0 = 1, FOE_= 0) = ROM 64-bit, SDRAM 64-bit               |

|        |                                      | $(MDL0 = 1, FOE_= 1) = ROM 8-bit, SDRAM 64-bit$              |

| MCP-,  | Sets the PCI output hold delay value | $(MCP_{-}=0, CKE=0)$                                         |

| CKE    | (in nanoseconds) relative to         | $(MCP_= 0, CKE = 1)$ Recommended for 33 MHz $PCI^{1,2}$      |

|        | PCI_SYNC_IN. Refer to the            | $(MCP_{-}=1, CKE=0)$                                         |

|        | MPC8245 documentation for details    | (MCP_ = 1, CKE = 1) Recommended for 66 MHz PCI               |

|        | on each setting.                     |                                                              |

| PMAA0, | Memory signal driver capabilities.   | (PMAA0 = 0, PMAA1 = 0) = reserved                            |

| PMAA1  |                                      | (PMAA0 = 0, PMAA1 = 1) = 40 Ω drive capability               |

|        |                                      | (PMAA0 = 1, PMAA1 = 0) = 20 Ω drive capability               |

|        |                                      | (PMAA0 = 1, PMAA1 = 1) = 6 Ω drive capability1,3             |

| PMAA2  | PCI and EPIC controller driver       | $0 = 40 \Omega$ drive capability <sup>1,2,3</sup>            |

|        | capabilities                         | $1 = 20 \Omega$ drive capability (except for IRQ2/S_RST and  |

|        |                                      | IRQ3/S_FRAME- signals which have 6 Ω drive                   |

|        |                                      | capability)                                                  |

| QACK-  | Clock Flip Disable                   | 0 = Clock flip enabled                                       |

|        |                                      | $1 = \text{No clock flip}^{1,2}$                             |

| GNT4-  | Debug Address Disable                | 0 = Debug address enabled                                    |

|        |                                      | 1 = Debug address disabled <sup>1,2</sup>                    |

| SDMA0  | DUART Signals Disabled               | 0 = DUART signals enabled                                    |

|        |                                      | 1 = PCI_CLK[0:3] signal used instead of DUART <sup>1,2</sup> |

| SDMA1  | Extended Addressing Mode             | 0 = Extended addressing mode enabled <sup>1,2</sup>          |

|        |                                      | 1 = Extended addressing mode disabled                        |

| RCS0-  | Boot Memory Location                 | 0 = Boot ROM is located on the PCI bus                       |

|        |                                      | 1 = Boot ROM is located on the local bus <sup>1,2</sup>      |

| MAA0   | Address Map Setting. The             | 0 = Invalid                                                  |

|        | MPC8245 only supports address        | $1 = MPC8245$ is configured for address map $B^{1,2}$        |

|        | map B.                               | Tr                                                           |

| MAA1   | PCI Host Mode                        | 0 = MPC8245 is a PCI agent device                            |

|        |                                      | 1 = MPC8245 is a PCI master device <sup>1,2</sup>            |

| MAA2   | PCI Arbiter Disable                  | 0 = PCI arbiter enabled <sup>1,2</sup>                       |

|        |                                      | 1 = PCI arbiter disabled                                     |

|        |                                      |                                                              |

Notes: 1. Bold indicates the recommended setting for the VX407C

- 2. 1=Switch OFF, 0=Switch ON (except for PMAA2 see note 3)

- 3. For the PMAA2 switch, 1=Switch ON, 0=Switch OFF

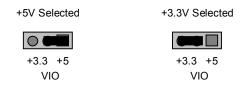

# 3.4.4 VIO Configuration Jumper

The VIO configuration jumper selects the voltage level supplied to the VIO pins on the PXI/cPCI connectors. The VIO power signals are used by universal CompactPCI modules that can operate in both +5V and +3.3V systems. On these boards, the power

for the I/O buffers is provided by the VIO pins instead of directly from the +3.3V or +5V power pins. Set the jumper according to the PXI/cPCI modules installed on the carrier as shown in Figure 8.

Figure 8 VIO Configuration Jumper

# 3.4.5 PPBV Configuration Jumper

The Processor PCI Bus Voltage (PPBV) configuration jumper selects the PCI bus voltage level. This is the active level at which the PowerPC will drive its PCI bus signals. The voltage level should be set according to the PXI/cPCI and PMC modules installed on the carrier. This voltage level will normally correspond to the VIO voltage level setting described in section 3.4.4. Figure 9 shows the PPBV configuration jumper settings.

Figure 9 PPBV Configuration Jumper

## 3.5 CONNECTORS

The VX407C incorporates several connectors to provide a physical connection to its various interfaces. Figure 4 shows the general location of each connector on the VX407C. Detailed pin-out information can be found in Appendix A. A short description of each connector is provided in the following sections.

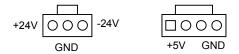

## 3.5.1 External Power Connectors

Two connectors are provided to connect +5V, +24V and -24V externally. The +5V connection is provided at a Molex 70543 male 4-pin connector. The +24V and -24V connections are provided by a Molex 70543 male 3-pin connector. Refer to Appendix A for details on the header pin-outs.

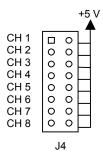

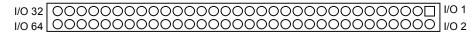

#### 3.5.2 External Drivers Connector

The external driver's output signals are available at a 16-pin header (8x2 with 0.100 inch centers). Refer to Appendix A for details on the header pin-outs.

#### 3.5.3 JTAG/COP Connector

Connection to the JTAG/COP debug interface is provided through a keyed 16-pin header (8x2 with 0.100 inch centers). This header is the standard size and employs the standard pin-out used by most JTAG based emulators. The pin-out details of the JTAG/COP header can be found in Appendix A.

# 3.5.4 PMC Connectors

The four PMC connectors provide the physical interface to a PMC module. The connectors are configured in accordance with the PMC specification. Refer to Appendix A for pin-out details.

## 3.5.5 PMC I/O Connector

Some PMC modules provide 64 bits of I/O to the PMC carrier board though the PMC rear connectors. On the VX407C these 64 bits of I/O are available at the PMC I/O connector. The connector is a standard 64 pin header (32x2 with 0.100 inch centers). Refer to Appendix A for pin-out details.

#### 3.5.6 VXI Connectors

The rear connectors, labeled P1 and P2, provide the physical interface to the VXI system. They are configured in accordance with the VXI specification. Refer to Appendix A for pin-out details.

#### 3.5.7 PXI/cPCI Connectors

The four PXI/cPCI connectors provide the physical interface for two 3U or one 6U PXI/cPCI modules. The connectors are configured in accordance with the PXI specification. Refer to Appendix A for pin-out details.

## 4.0 SYSTEM ARCHITECTURE

## 4.1 OVERVIEW

The system architecture illustrated in Figure 3 is viewed differently from an application running on the embedded PowerPC than from an application running on the VXI host. Most of the carrier's hardware can be accessed by both applications but, the methods for doing so differ. The system architecture is best described by viewing the host-side and the device-side separately. However, it is also important to understand how the resources shared between both applications are used for host to device communications.

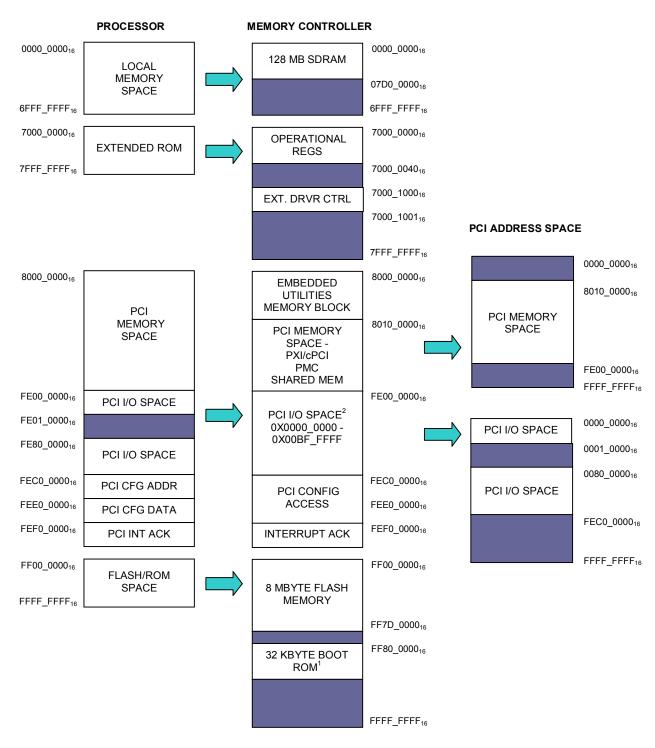

## 4.2 DEVICE-SIDE ARCHITECTURE

The device-side architecture is anchored by a standard embedded processor system powered by the MPC8245 PowerPC. The architecture provides on-board RAM, boot ROM, and flash memory to support the software application. The PowerPC acts as the PCI bus master and has full access to all devices on the PCI bus. A set of operational registers and the external relay driver are available to the application via the processor's local bus. Figure 10 illustrates the device-side architecture.

Figure 10 Device-Side Architecture

# 4.2.1 PowerPC Memory Map

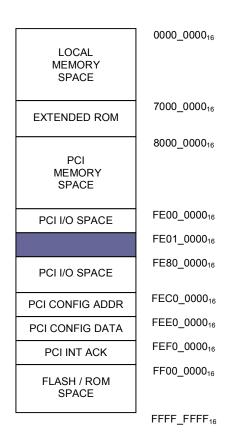

Being a 32-bit processor, the MPC8245 can address up to 4 Gigabytes of physical memory. On the VX407C, the processor maps this 4 Gigabytes of memory into a configuration designated as Address Map B. The address map B configuration divides the memory space into sections that, when accessed, translate the operation to a local memory, PCI memory, PCI I/O, or ROM access. Figure 11 shows the general layout of address map B.

Figure 11 Address Map Overview

Details of the address map B implementation for the VX407C architecture are shown in Figure 12. Each section in the address map directly addresses a resource in the system architecture. Further details of each address block are provided throughout this document. Other address map B options and settings are also available but generally not used on the VX407C. Refer to the MPC8245 User's Manual for details.

#### Notes:

- 1. The boot ROM device only decodes 15 address lines. Therefore, the boot ROM is repeated throughout the address space. For example, address FF80 0000<sub>16</sub> is the same location as FFF0 0000<sub>16</sub>.

- PCI I/O accesses are forwarded to the PCI bus with the 8 most significant bits of the address cleared. (i.e. processor address FE80\_0000<sub>16</sub> = PCI I/O address 0080\_0000<sub>16</sub>)

Figure 12 Detailed PowerPC Address Map

#### 4.2.2 SDRAM

The SDRAM provides 128 Megabytes of temporary storage for the application. The memory is organized in a 13 rows x 10 columns x 4 banks configuration. It has a 10ns access time and a 32 bits wide data bus. It is accessed through the PowerPC's addresses space starting at offset 0.

#### 4.2.3 Boot ROM

The boot ROM provides 64 kilobytes of non-volatile, read-only memory. It is normally programmed during the manufacturing process to contain boot code and initialization routines. It can not be reprogrammed in circuit. The boot ROM is mapped to PowerPC address FF80\_0000<sub>16</sub> and has an 8-bit data bus. Only 15 address bits are decoded so that the 64 kilobytes are repeated throughout the PowerPC's ROM/Flash space between addresses FF80\_0000<sub>16</sub> and FFFF\_FFFF<sub>16</sub>. Consequently, the default exception vector table starting at address FFF0\_0000h resides in the boot ROM device.

# 4.2.4 Flash Memory

The flash device provides 8 megabytes of non-volatile storage for code and data. Unlike the boot ROM, flash is programmable in circuit and may be used by a user application. However, the first sector is normally reserved for use by the system firmware. The flash device is accessed starting at PowerPC address FF00\_0000<sub>16</sub> and has an 8-bit wide data bus. Reads from flash are performed as standard PowerPC memory accesses. Programming and erasing the device, however, requires a sequence of commands to be sent to the device. System utilities are provided with the on-board system routines for programming the flash device. For details on using the on-board system utilities refer to section 5.2.

## 4.2.5 PCIbus Architecture

The on-board PCI bus can contain up to 5 devices including the PowerPC which acts as the bus master. If a PCI to PCI Bridge is added at any of the PCI interfaces, more devices are available and can be accessed by the PowerPC. The devices on the primary bus include the PowerPC, the shared memory device, a PMC device, and the PXI/cPCI devices. The bus operates at 33 MHz and 5V or 3.3V (jumper selectable).

PCI memory, configuration, and I/O space is memory mapped directly into the PowerPC's address map as shown in Figure 12. Approximately 2 gigabytes of PCI memory space is mapped starting at address 8010\_0000<sub>16</sub>. Each device requiring memory will have a base address within this mapped area. About 4 megabytes of PCI I/O space is mapped to PowerPC addresses FE00\_0000<sub>16</sub>. When performing a PCI I/O access, the processor clears the upper 8 bits of the address before forwarding the transaction to the

PCI bus. So, for example, accessing processor address FE80 $\_0000_{16}$  will read or write PCI I/O address  $0080\_0000_{16}$ . The base address of each device is determined by the PCI enumeration routines during initialization. The base address of a particular device can be determined by reading its Base Address Register (BAR) register in PCI configuration space for that device.

To perform a single PCI configuration write or read, two processor accesses are required. First, the PCI configuration address register at PowerPC address FEC0\_0000<sub>16</sub> must be set to point to the correct device and offset. Then the data can be read from or written to the PCI configuration data register at PowerPC address FEE0\_0000<sub>16</sub>. The PCI configuration address register value is determined by the device number, IDSEL signal routing, device function number, and the register offset. For details on performing PCI configuration accesses refer to the MPC8245 User's Manual. System routines are provided that an application can use to perform configuration reads and writes. For details on using the on-board system utilities for configuration accesses, refer to section 5.2.

## 4.2.5.1 PCIbus Enumeration

During initialization, the boot-up firmware will search the PCI bus for devices, determine the resources needed for the device, and allocate the resources accordingly. This procedure determines where in the PowerPC memory map a particular PCI device's memory space is located. PCI device mapping is not guaranteed from one carrier configuration to another or even from one firmware version to another. The application software should always check a device's configuration registers for memory mapping information prior to accessing the device.

# 4.2.5.2 IDSEL Signal Routing

Each device on the PCI bus has a unique ID select line used to specify the destination of a configuration access. The PCI specification does not stipulate the source of each ID select line; however, the upper 16-bits of the address bus are normally used. On the VX407C each device has its IDSEL line tied to a specific address line as shown in Table II. The device number, normally provided to software routines, is also system dependant. Table II also shows the device numbering used on the VX407C. This information must be incorporated into a configuration access by the application when performing a write or read. The system routines for configuration access automatically incorporate this information into the access.

**Table II IDSEL Signal Routing**

| Device                   | IDSEL | DevNum           |

|--------------------------|-------|------------------|

| Shared Memory            | AD16  | $16_{10}$        |

| PowerPC                  | AD17  | 17 <sub>10</sub> |

| • PMC                    | AD18  | 18 <sub>10</sub> |

| PXI Slot A (bottom slot) | AD31  | $10_{10}$        |

| PXI Slot B (top slot)    | AD30  | $30_{10}$        |

# 4.2.5.3 PCI Interrupts

The PowerPC's Embedded Programmable Interrupt Controller (EPIC) acts as the PCI interrupt controller. The interrupt lines from the PCI devices are routed to the EPIC controller's five interrupt inputs as shown in Table III. The PCI specification requires that single function devices only use interrupt pin INTA#. Thus, in most cases, each device on the VX407C's PCI bus will have a unique interrupt line to the EPIC controller. Only in the rare case where a multi-function device is to be used will interrupt line sharing be required. Refer section 6.5.1 of this document and the MPC8245 User's Manual for information on programming the EPIC controller to handle interrupts.

**Table III PCI Interrupt Signal Routing**

| Device        | PCI Interrupt Pin | EPIC IRQ |

|---------------|-------------------|----------|

| PXI-A         | INTA#             | IRQ1     |

| (Bottom Slot) | INTB#             | IRQ2     |

|               | INTC#             | IRQ3     |

|               | INTD#             | IRQ0     |

|               |                   |          |

| PXI-B         | INTA#             | IRQ2     |

| (Top Slot)    | INTB#             | IRQ3     |

|               | INTC#             | IRQ0     |

|               | INTD#             | IRQ1     |

|               |                   |          |

| PMC           | INTA#             | IRQ3     |

|               | INTB#             | IRQ0     |

|               | INTC#             | IRQ1     |

|               | INTD#             | IRQ2     |

|               |                   |          |

| Shared Memory | INTA#             | IRQ4     |

|               |                   |          |

Note: Bold indicates the EPIC interrupt line unique to the device when no multi-function devices are in use.

# 4.2.5.4 Shared Memory Device

The shared memory's entire address space is mapped to PCI memory space including all operations registers, the I<sub>2</sub>O messaging unit, and the general purpose shared memory. The offset into PowerPC memory space is determined at boot up by the PCI enumeration software.

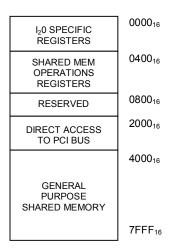

Figure 13 shows the shared memory device's address map. All addresses are offsets from the devices base address. To determine the shared memory's base address perform a PCI configuration read of offset  $10_{16}$  (BAR0 Register) of the shared memory's configuration space. This value is the base address of the shared memory device. The general purpose shared memory begins at an offset of  $4000_{16}$  from this address.

Figure 13 Shared Memory Organization

#### 4.2.5.5 PXI/cPCI Devices

The two PXI/cPCI positions reside on the on-board PCI bus. Any memory or I/O space required by a device connected to one of these two slots is mapped to the PowerPC's address space. These devices may also contain a PCI to PCI Bridge in which case devices on the PXI/cPCI module's secondary bus will also be mapped to the PowerPC's address space.

PXI defined signals not specified by the PCI or CompactPCI specifications are also provided by the carrier. The PXI TTL triggers can be mapped directly to any of the VXI TTL triggers as discussed in section 4.2.6. The carrier also includes a 10 MHz clock source to provide the PXI\_CLK\_10 signal to the PXI connectors. Start trigger operation is supported with slot B (top slot) pin-outs configured to accept a PXI start trigger module.

#### 4.2.5.6 PMC Device

The PMC position resides on the on-board PCI bus. Its address space is mapped directly to the PowerPC's address map. The bus mode signals are implemented to inform the PMC module of the PCI bus configuration. The PMC module may contain a PCI to PCI Bridge whose secondary bus is fully accessible by the PowerPC. Interrupts from the PMC device are supported as described in section 4.2.5.3.

# 4.2.6 Triggers

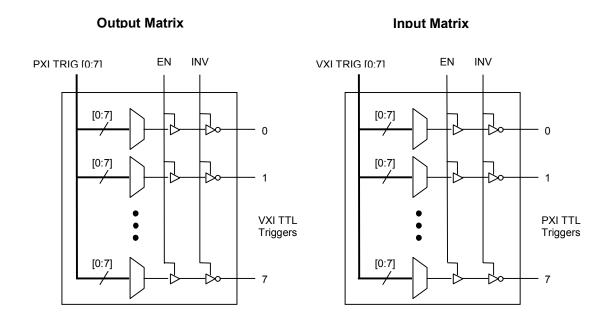

The carrier includes two programmable switching matrices for mapping PXI triggers to VXI triggers. The matrices are illustrated in Figure 14. The input matrix operates in the direction from the VXI system to the PXI module while the output matrix operates in the direction from the PXI module to the VXI system. In each direction the trigger can be enabled or disabled and inverted.

This architecture provides enormous flexibility allowing a large number of trigger mapping combinations. Programming of the matrices is provided via the operations registers discussed in section 4.2.7 and detailed in section 4.4.1.

**Figure 14 Trigger Architecture**

#### 4.2.7 Operations Registers

A set of operations registers are defined to allow the user application or the host application to perform certain operations on the VX407C such as PXI to VXI trigger mappings. The standard set of VXI defined registers are also part of the operations registers. The PowerPC has access to these operations registers via the local bus. These registers are mapped to the PowerPC's extended ROM space starting at address 7000\_0000<sub>16</sub>. The data bus width between the PowerPC and the operations registers is 8-bits wide and reads and writes are performed as standard memory accesses. For register definitions in this space refer to section 4.4.1.

#### 4.2.8 External Drivers

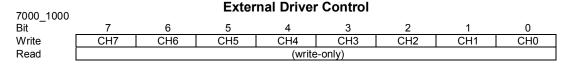

The architecture includes an 8-bit Darlington sink driver device residing on the PowerPC's local memory bus. The device is intended to drive external relays, display LED's, or other devices with high current requirements. The device's outputs are available at a 16 pin header for external use. Refer to section 3.5.2 and Appendix A for details on the header

Access to the device is provided at address 7000\_1000<sub>16</sub>. The data bus width to the device is 8-bits wide and each bit corresponds to one of the 8 channels. The device can only be written to. Figure 15 shows the external driver control register.

CHx  $\Rightarrow$  Channel value (1 = driven, 0 = not drivern)

Note: On VX407C Revision A modules, reading this register will cause random data to be written to the relay driver.

Figure 15 External Driver Control Register

#### 4.2.9 JTAG/COP Interface

The JTAG interface to the PowerPC provides support for several standard off-the-shelf developments tools. Most development environments for the PowerPC support JTAG based communications with the processor. It provides the developer with the ability to view system registers, view memory, set breakpoints, and use other standard debugging practices.

Connection to the JTAG/COP interface is provided through a standard 16 pin header. Refer to section 3.5.3 and Appendix A for details on the header.

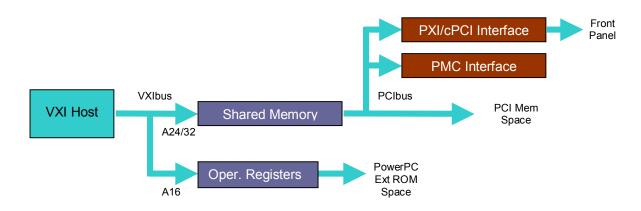

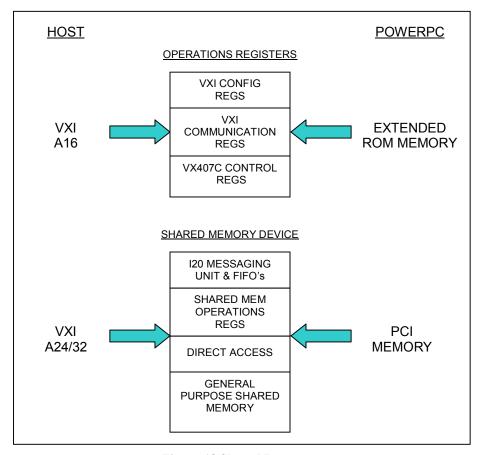

#### 4.3 HOST-SIDE ARCHITECTURE

The host-side architecture is anchored by the VXI system including a VXI chassis and a host computer. Standard off-the-shelf VXI controllers from several different manufacturers are available to interface the carrier to the host computer, including high performance embedded controllers. The VXI host has access to the entire address space of the shared memory device as well as to a set of the operations registers. The shared memory device provides a utility to directly access devices on the PCI bus from the VXI host. Therefore, the VXI host application can control on-board PCI devices without the assistance of the PowerPC. The standard VXI registers required by the VXI specification are implemented as part of the operations registers. These include the registers required to implement the VXI word serial protocol. The VXI host has the ability to fully access all devices on the on-board PCI bus and to fully utilize all host to device communications utilities. Figure 16 illustrates the intelligent carrier architecture as viewed from the VXI host computer.

**Figure 16 Host-Side Architecture**

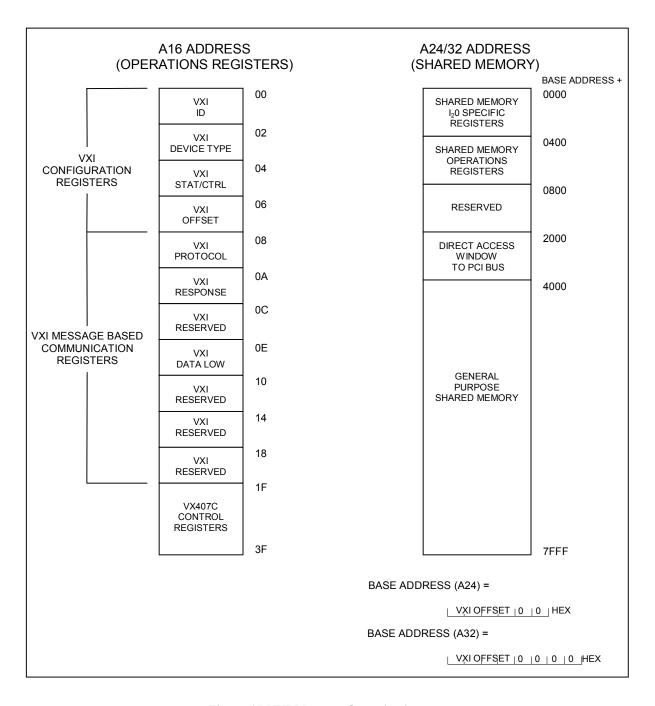

# 4.3.1 VXI Memory Map

Figure 17 shows the host-side memory organization for the intelligent carrier. The operations registers are accessed via VXI A16 space. These registers include the VXI required registers and the VXI message based communication registers as defined by the VXIbus specification.

A24/A32 memory space is a direct mapping of the shared memory device's memory map. This architecture gives the host full access to the shared memory and its registers including direct access to the PCI bus and other miscellaneous communications utilities.

A24 or A32 addressing is switch selectable as described in section 3.4.2. The VXI resource manager will write a base address to the offset register at address  $06_{16}$  in A16 space. If the carrier is configured for A32 addressing the carrier will use the value of the offset register as the upper 16 bits of its 32-bit base address. If A24 addressing is selected the carrier will use the value in the offset register as the upper 16 bits of its 24-bit base address. This behavior is illustrated at the bottom of Figure 17.

Figure 17 VXI Memory Organization

#### 4.3.2 Data Bus Width

The intelligent carrier supports 16 and 32-bit wide data transactions to the shared memory device in the A24/A32 address space. However the device must be configured to be either 16 or 32-bits, but not both. Differences in the byte lane assignments between the VXI bus and the shared memory's local bus make dynamically switching between D16 and D32 impossible.

A system command is provided to configure the data bus width to the shared memory device. Refer to section 5.2.7 for details on the configuration command. A system configuration option is also provided allowing the data bus width setting to be initialized to the desired value at reset. Refer to section 5.2.2 for details on configuration options.

Only 16-bit accesses to A16 address space are supported.

#### 4.3.3 PCI Bus Mastering and Direct Access

The shared memory device provides an 8 Kilobyte window directly into PCI memory space. This window is accessible by the VXI host at offset 2000<sub>16</sub> in A24/A32 space. This window gives the host PC direct access to any PCI device residing on the on-board PCI bus as well as any secondary buses that may exist. To point the 8 Kilobyte window to the correct PCI bus address the host must control the direct access control register defined by the shared memory device. The register is part of the shared memory operation registers accessible by the VXI host in A24/A32 space. Refer to section 6.8 for details on using the direct access capabilities of the carrier.

#### 4.4 SHARED RESOURCES AND DEVICE COMMUNICATIONS

Communication between the host-side application and the device-side application is accomplished using a couple of resources available to both the host and the device. Namely, these shared resources are the operations registers and the shared memory device as shown in Figure 18. These shared resources are used to perform VXI communications, device configurations, block data transfers, and other miscellaneous functions.

**Figure 18 Shared Resources**

#### 4.4.1 Operations Registers

The operations registers combine the required VXI configuration registers, VXI communication registers and a set of carrier control registers. Table IV lists all available registers along with their offset. The VXI host can access each registers at its specified offset in the A16 address space. The PowerPC can access each register at its specified offset in its extended ROM space starting at address 7000\_0000<sub>16</sub>. There maybe access restrictions on individual registers or individual bits within a register depending on the whether it is being accessed by the host-side or the device-side application. Refer to the register descriptions in Figure 19, Figure 20, and Figure 21 for details on each register.

The PowerPC's interface to the operations registers is only 8-bits wide. In Figure 19, Figure 20, and Figure 21, the least significant bits reside in the low PowerPC address. For example, VXI ID bits 0-7 reside at PowerPC address 0x7000\_0000<sub>16</sub> and bits 8-15 reside at address 0x7000\_0001<sub>16</sub>.

**Table IV Operations Registers Map**

| Offset  | Register Description    |

|---------|-------------------------|

| VXI     | Configuration Registers |

| 00      | VXI ID                  |

| 02      | VXI Device Type         |

| 04      | VXI Status/Control      |

| 06      | VXI Offset Register     |

| VXI C   | ommunication Registers  |

| 08      | VXI Protocol            |

| 0A      | VXI Response            |

| 0C      | Reserved                |

| 0E      | VXI Data Low            |

| 10 – 1F | Reserved                |

| VX4     | 07C Control Registers   |

| 20      | VX407C Status/Control   |

| 22      | Interrupt Control       |

| 24      | Trigger Control         |

| 26-3F   | Reserved                |

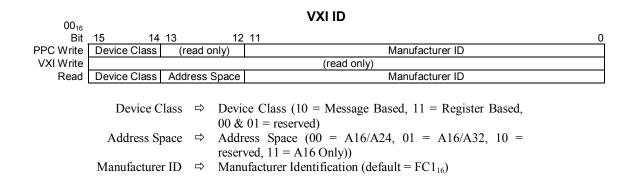

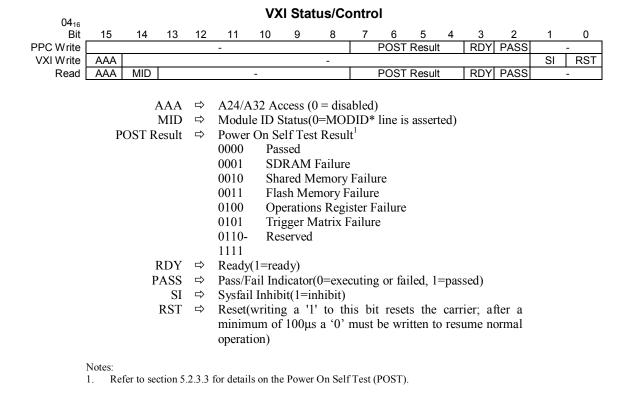

### 4.4.1.1 VXI Configuration Registers

The VXI configuration registers contain basic information needed to configure a VXI system as required by the VXIbus specification. The configuration information includes: manufacturer identification, product model code, device type, memory requirements, device status, and device control. The registers are briefly described below and are detailed in Figure 19.

<u>VXI Identification (ID) Register</u> (00<sub>16</sub>): This register provides the manufacturer identification, device classification (i.e., register based or message based), and the addressing mode (i.e. A32 or A24). It is a read only register from the VXI host. The PowerPC can write this register however it should be done immediately after reset prior to running VXI resource manager. System configuration options are available to initialize this register automatically after reset. Refer to section 5.2.2 for details on the configuration options.

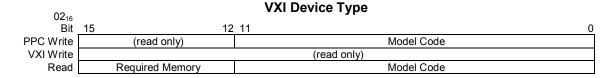

<u>VXI Device Type Register</u> (02<sub>16</sub>): This register provides the model code identifier and required memory information. It is a read only register from the VXI host. The PowerPC can write this register however it should be done immediately after reset prior to running VXI resource manager. System configuration options are available to initialize this register automatically after reset. Refer to section 5.2.2 for details on the configuration options.

<u>VXI Status/Control Register</u> (04<sub>16</sub>): A read of this register provides the state of the VXI MODID\* line and the pass, ready, and self-test status bits. A write to this register allows

disabling of the SYSFAIL function and performing a reset of the carrier. This register is readable and writeable from both the VXI host and the PowerPC however, there are several access restrictions on individual bits depending on the source of the access.

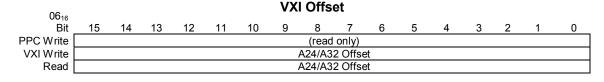

<u>VXI Offset Register</u> (06<sub>16</sub>): This register controls the offset value for addressing the A24/A32 address space. The VXI system resource manager or control module sets this value according to the memory requirements specified for this module and the memory requirements of the other instruments in the system. This register is readable and writeable from the VXI host. The PowerPC only has read capability of this register.

Required Memory  $\Rightarrow$  32 Kbytes required (F<sub>16</sub> if A32, 8<sub>16</sub> if A24) Model Code  $\Rightarrow$  Model Code (default = FE4<sub>16</sub>)

Figure 19 VXI Configuration Registers

A24/A32 Offset ⇒ Offset to the carriers A24/A32 memory space

Figure 19 VXI Configuration Registers (continued)

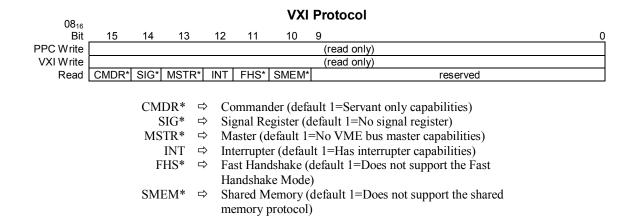

# 4.4.1.2 VXI Communication Registers

The VXI communication registers are defined by the VXI specification for message based devices. They provide all the functionality necessary to perform the VXI word serial protocol. The word serial protocol firmware in the on-board system utilities manages these registers to perform message passing. Only on very rare occasions should the user application need to access these registers directly. Figure 20 shows these registers in detail.

CAUTION: It is rarely necessary for either the host-side or the device-side application to access the VXI communications registers directly. The host-side VXI libraries and the device-side on-board system utilities automatically manage these registers when performing message passing functions. Directly accessing these registers is not advised without prior knowledge of the VXI specification for message based devices.

<u>VXI Protocol Register</u> ( $08_{16}$ ): This register indicates which message based protocols the carrier supports and indicates additional communication capabilities of the carrier. This register is a read only register by both the host and device applications.

<u>VXI Response Register</u> (0A<sub>16</sub>): This register indicates status of the carrier's communications capabilities. The register is read only from the host-side application. The PowerPC writes to this register to perform message passing. The PowerPC user application should never need to write to this register. The word serial protocol handler in the on-board system utilities automatically manages this register.

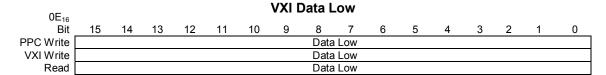

<u>VXI Data Low Register</u> (0E<sub>16</sub>): This register is used to pass VXI commands and data to and from the carrier over the VXI bus. A write to this register causes the word serial protocol handler in the on-board system utilities to execute and handle the command. The status of this register is indicated in the VXI response register. This register is readable and writeable by both the host and device applications. However, the rules for message based communications as set by the VXI specification must be followed to ensure data integrity. Neither the PowerPC nor the VXI host applications should need to write directly to this register. The word serial protocol handler in the on-board system utilities automatically manages this register and the VXI host should use standard VXI libraries to communicate with the carrier.

#### **VXI Response** 0A<sub>16</sub> 15 13 10 Bit 14 12 11 LCK\* PPC Write WRDY FHS\* 0 DOR DIR ERR\* RRDY rsvd reserved VXI Write (read only) Read rsvd DOR DIR ERR\* RRDY WRDY FHS\* LCK\* reserved DOR Data Out Ready (1 = message byte available to be read by VXI host)

| DIR  | $\Rightarrow$ | Data In Ready ( $I = carrier ready to receive message$        |

|------|---------------|---------------------------------------------------------------|

|      |               | byte)                                                         |

| ERR* | $\Rightarrow$ | Error ( $0 = \text{error occurred}, 1 = \text{no error}$ )    |

| RRDY | $\Rightarrow$ | Read Ready ( $1 = \text{data has been place in the data low}$ |

|      |               | register for read by the VXI host) <sup>1</sup>               |

| WRDY | $\Rightarrow$ | Write Ready $(1 = data low register is empty and ready)$      |

|      |               | for VXI host to write a command) <sup>2</sup>                 |

| FHS* | $\Rightarrow$ | Fast Handshake Active ( $0 = \text{Fast handshake mode is}$   |

|      |               | active)                                                       |

| LCK* | $\Rightarrow$ | Locked ( $0 = a$ commander has locked the carrier from        |

### Notes:

- The read ready bit automatically cleared by the VXI interface logic when the data low register is read by the VXI host.

- The write ready bit is automatically cleared by the VXI interface logic when the data low register is written by the VXI host.

being accessed by other sources)

Figure 20 VXI Communications Registers

#### Notes:

- The VXI specification for message based devices must be followed for reading and writing the data low register

- 2. The read ready bit in the VXI response register is automatically cleared by the VXI interface logic when the data low register is read by the VXI host.

- The write ready bit in the VXI response register is automatically cleared by the VXI interface logic when the data low register is written by the VXI host.

Figure 20 VXI Communications Registers (continued)

### 4.4.1.3 VX407C Control Registers

The VX407C control registers provide miscellaneous configuration, status, and control functionality for the carrier. Refer to the register descriptions and Figure 21 for details.

<u>VX407C Control/Status</u> (20<sub>16</sub>): This register provides miscellaneous status information and control functionality for the carrier. Each bit has individual read/write restrictions depending on whether the host-side or the device-side application is accessing it.

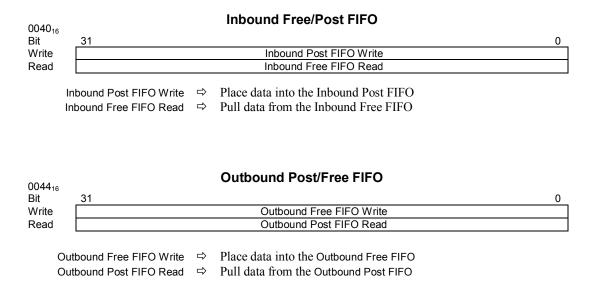

<u>Interrupt Control</u> (22<sub>16</sub>): This register is used by the PowerPC application to interrupt the VXI host. The host or PowerPC application can enable/disable the ability of the carrier to interrupt the VXI host and can configure the interrupt level. The PowerPC application can set a vector that'll be passed to the VXI host and generate the interrupt.